# **Design Aspects of Software Distributed Shared Memory Components and Implementation**

A thesis submitted to the University of Hyderabad in partial fulfillment of the requirements for the award of

# **Doctor of Philosophy**

in

## **Computer Science**

by

R. Sitharamaiah

Reg. No: 06MCPC06

School of Computer and Information Sciences

University of Hyderabad

Hyderabad - 500 046

Andhra Pradesh, India

August 2013

#### **CERTIFICATE**

This is to certify that the thesis entitled "**Design Aspects of Software Distributed Shared Memory Components and Implementation**" submitted by **R. Sitharamaiah** bearing Reg. No: **06MCPC06** in partial fulfillment of the requirement for the award of Doctor of Philosophy in Computer Science is a bonafide work carried out by him under my supervision and guidance.

The thesis has not been submitted previously in part or in full to this or any other University or Institution for the award of any degree or diploma.

Dr. Rajeev Wankar Associate Professor School of Computer and Information Sciences University of Hyderabad Hyderabad - 500 046

Prof. Arun K. Pujari

Dean

School of Computer and Information Sciences

University of Hyderabad

Hyderabad - 500 046

**DECLARATION**

I, R. Sitharamaiah, hereby declare that this thesis entitled "Design Aspects of

Software Distributed Shared Memory Components and Implementation"

submitted by me under the guidance and supervision of Dr. Rajeev Wankar is a

bonafide research work. I also declare that it has not been submitted previously in part

or in full to this or any other university or institution for the award of any degree or

diploma.

Date: 01/08/2013

Name: R. Sitharamaiah

Reg. No. 06MCPC06

iii

#### Acknowledgement

First of all I express my profound gratitude and deep regards to my supervisor, Dr. Rajeev Wankar. I'm grateful to him for all the motivating discussions right from selection of research problem to timely guidance at every moment. My gratitude towards him is very small when compared to the support and guidance received from him. I also thank Prof C.R. Rao for his innovative research ideas and realization of concepts, which helped my research.

I gratefully acknowledge my DRC members Prof. Arun Agarwal for his continuous monitoring and valuable directions and mid-course corrections in my research progress. I also thank Dr. Atul Negi for his valuable suggestions. I learned many useful insights from their interactions in my DRCs.

I would like to express my sincere gratitude to the Dean, Prof. A.K. Pujari, School of Computer and Information Sciences, for his cooperation.

I am thankful to faculty of our school, whose interactions made my research complete. I also thank the technical and office staff of AI lab and our school for their cooperation.

My special thanks to my friends and research scholars in our school, especially Mr. P.S.V.S.Sai Prasad, Dr. N. Naveen, Mr. B.Vikranth and M.Raghava for their encouragement and support is invaluable, I will forever be thankful to them.

I express my gratitude to Management of CVR College of Engineering, Hyderabad in particular Advisor Prof.C. Mahusudhan Reddy, Hyderabad for granting multiple study leaves and encouragement, which helped in pursuing research. I acknowledge my colleagues for their cooperation.

The past seven years have not been an easy ride, both academically and personally. I truly thank my family members for their constant encouragement. It would not have been possible to write this doctoral thesis without the help and support of the kind

people around me, to only some of whom it is possible to give particular mention here. Finally, I thank all of them.

Hyderabad R. Sitharamaiah

Date: 01/08/2013

# **Table of Contents**

| Declaration     |                                                | iii |

|-----------------|------------------------------------------------|-----|

| Acknowledge     | ment                                           | iv  |

| List of Figures | S                                              | xi  |

| List of Tables  |                                                | xii |

| List of Publica | ations                                         | xiv |

| Abstract        |                                                | XV  |

| 1.0 Introduc    | tion                                           | 1   |

| 1.1 Int         | roduction                                      | 1   |

| 1.2 Dis         | stributed Shared Memory                        | 2   |

|                 | 1.2.1 SDSM Taxonomy reference                  | 6   |

| 1.3 He          | terogeneous Distributed Shared Memory          | 8   |

|                 | 1.3.1 HDSM Taxonomy reference                  | 8   |

| 1.4 Mo          | otivation and Objective                        | 10  |

| 1.5             | Research Problems Related to Objectives        | 11  |

|                 | 1.5.1 HDSM Framework                           | 11  |

|                 | 1.5.2 Hierarchical Thread Pool Executor (HTPE) | 12  |

|                 | 1.5.3 Dynamic Pre-fetching Strategies          | 13  |

|                 | 1.5.4 Parallelization of N-gram Model          | 13  |

| 1.6 Re          | search Contributions                           | 14  |

| 2.0 Literatu    | re Survey                                      | 16  |

| 2.1 Di          | stributed Shared Memory Systems                | 16  |

|                 | 2.1.1 Software Distributed Shared Memory       | 16  |

|                 | 2.1.2 Compiler Based SDSMs                     | 25  |

|     | 2.1.3 Hardware Distributed Shared Memory Systems            | 31 |

|-----|-------------------------------------------------------------|----|

|     | 2.1.4 Hybrid Distributed Shared Memory Systems              | 33 |

|     | 2.2 Heterogeneous Distributed Shared Memory Systems         | 35 |

|     | 2.3 Process Migration/Thread Migration                      | 39 |

|     | 2.4 Checkpointing                                           | 40 |

|     | 2.5 Thread Pool Executor Related                            | 42 |

|     | 2.6 Prefetching Related                                     | 43 |

|     | 2.7 N-Gram based Language Models                            | 49 |

| 3.0 | Hierarchical Thread Pool Executor                           | 53 |

|     | 3.1 Introduction                                            | 53 |

|     | 3.2 Motivation for Hierarchical Thread Pool Executor (HTPE) | 55 |

|     | 3.3 Thread Pool Executor                                    | 56 |

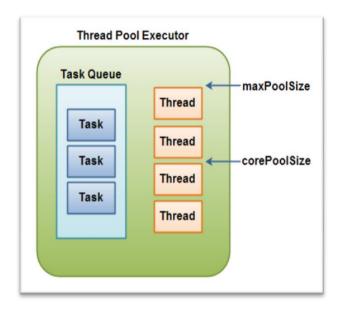

|     | 3.3.1 Core and maximum pool sizes                           | 57 |

|     | 3.3.2 Benefits of Thread Pooling                            | 58 |

|     | 3.3.3 Problems of Thread Pooling                            | 59 |

|     | 3.4 Design                                                  | 60 |

|     | 3.5 Hierarchical Thread Pool Algorithm                      | 62 |

|     | 3.6 Non-Blocking Queues                                     | 64 |

|     | 3.6.1 Introduction                                          | 64 |

|     | 3.6.2 Implementation Aspects of Non-Blocking Queues         | 65 |

|     | 3.6.2.1 Creation of Threads                                 | 67 |

|     | 3.6.3 Defining a Non-Blocking Queue Data Structure          | 67 |

|     | 3.6.4 Insertion into a Non-Blocking Queue                   | 68 |

| 3.6.5 Sorting in a Non-Blocking Queue                   | 69 |

|---------------------------------------------------------|----|

| 3.6.6 Deletion from a Non-Blocking Queue                | 70 |

| 3.6.7 Binary Min-Heap Implementation                    | 70 |

| 3.6.8 Execution of Threads                              | 72 |

| 3.7 Thread Migration Implementation with HTPE based RTS | 74 |

| 3.8 Testing of HTPE With Standard Benchmark Programs    | 74 |

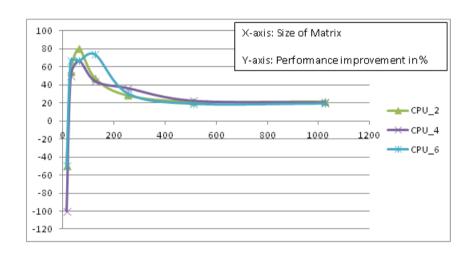

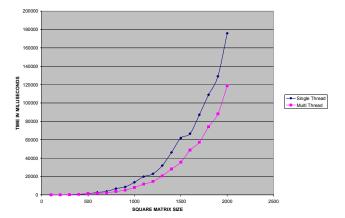

| 3.8.1 Testing of MATMUL with HTPE                       | 74 |

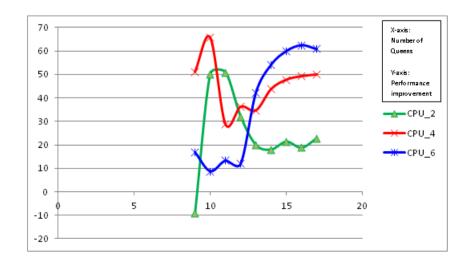

| 3.8.2 Testing n-queens with HTPE                        | 76 |

| 3.8.3 Testing HTPE with Boolean Satisfiability          | 77 |

| 3.9 Conclusions                                         | 78 |

| Chapter 4: Dynamic Pre-fetching Strategies              | 79 |

| 4.1 Introduction                                        | 79 |

| 4.2 Pre-fetching                                        | 79 |

| 4.2.1 Hardware Pre-fetching                             | 81 |

| 4.2.2 Software Pre-fetching                             | 81 |

| 4.2.3 Model based Pre-fetching                          | 83 |

| 4.3 Necessity of Pre-fetching in DSM                    | 84 |

| 4.4 Motivation for n-gram based model                   | 84 |

| 4.5 n-gram model                                        | 85 |

| 4.6 n-gram model based pre-fetching                     | 86 |

| 4.6.1 Language Models                                   | 86 |

| 4.6.2 n-gram Model Application to Stride Pre-fetching   | 89 |

|                    | 4.6.3 Computation and Importance of Conditional Probab | bility |

|--------------------|--------------------------------------------------------|--------|

|                    | Transition Matrix (CPTM)                               | 93     |

| 4.7 Dy             | ynamic Pre-fetch Algorithm                             | 98     |

| 4.8 Re             | esult and Discussion                                   | 99     |

|                    | 4.8.1 Testing with applications                        | 99     |

| 4.9                | Conclusions                                            | 104    |

| Chapter 5: Pa      | arallelization of n-gram Model                         | 105    |

| 5.1 Int            | troduction                                             | 107    |

| 5.2 PF             | RAM model                                              | 107    |

| 5.3 Fi             | ne grain parallelism in n-gram model                   | 109    |

| 5.4 Pa             | rallel n-gram Algorithm                                | 110    |

|                    | 5.4.1 Parallel algorithm Complexity                    | 111    |

| 5.5 Illu           | astration Creation of grams                            | 112    |

|                    | 5.5.1 1-gram sequence generation                       | 113    |

|                    | 5.5.2 2-gram to n-gram Sequence generation             | 115    |

|                    | 5.5.3 Count and Conditional Probability Computation    | 119    |

|                    | 5.5.4 Generation of n-gram sequence                    | 120    |

| 5.6 Int            | tegration of n-gram model in SDSM and Conclusion       | 122    |

| 6: Heterogen       | eous DSM Architectural Framework                       | 124    |

| 6.1 Int            | roduction                                              | 124    |

| 6.2 No             | eed for Unified HDSM framework                         | 124    |

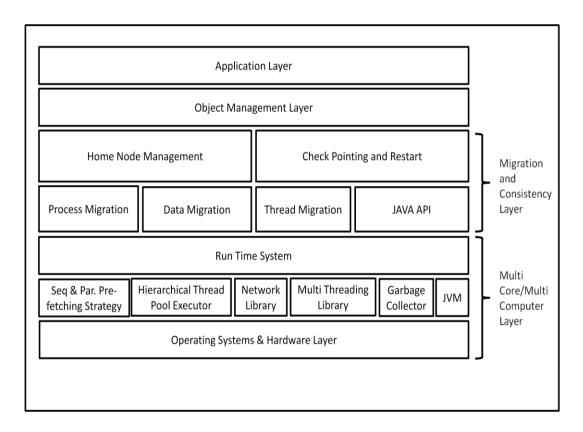

| 6.3 Co             | omponents of Framework                                 | 125    |

| 6.4 A <sub>I</sub> | pplication Layer                                       | 126    |

| 6.5 Object Management Layer                    | 126 |

|------------------------------------------------|-----|

| 6.6 Migration and Consistency Layer            | 127 |

| 6.6.1 Home Node Management                     | 128 |

| 6.6.2 Checkpointing and Restart                | 128 |

| 6.6.3 Process Migration                        | 129 |

| 6.6.4 Data Migration                           | 130 |

| 6.6.4.1 Data Conversion                        | 131 |

| 6.6.5 Thread Migration                         | 132 |

| 6.7 Multi-Core Operations Layer                | 133 |

| 6.7.1 Run Time System (RTS)                    | 133 |

| 6.7.2 Network Library                          | 134 |

| 6.7.3 Multi-Threaded Libraries                 | 135 |

| 6.7.4 Garbage Collector (GC)                   | 135 |

| 6.7.5 Hierarchical Thread Pool Executor (HTPE) | 136 |

| 6.7.6 Dynamic pre-fetching strategies          | 137 |

| 6.8 Operating System/Hardware Layer            | 137 |

| 6.9 Conclusion                                 | 138 |

| 7. Conclusion and Future Work                  | 139 |

| 7.1 Conclusion                                 | 139 |

| 7.2 Future Work                                | 140 |

| Bibliography                                   |     |

| Annexure A: Published Papers from the thesis   |     |

# **List of Figures**

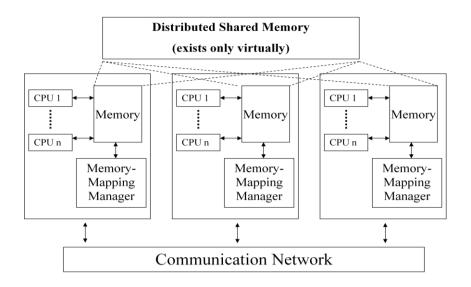

| Figure 1.1 | A representative diagram showing DSM                        | 3   |

|------------|-------------------------------------------------------------|-----|

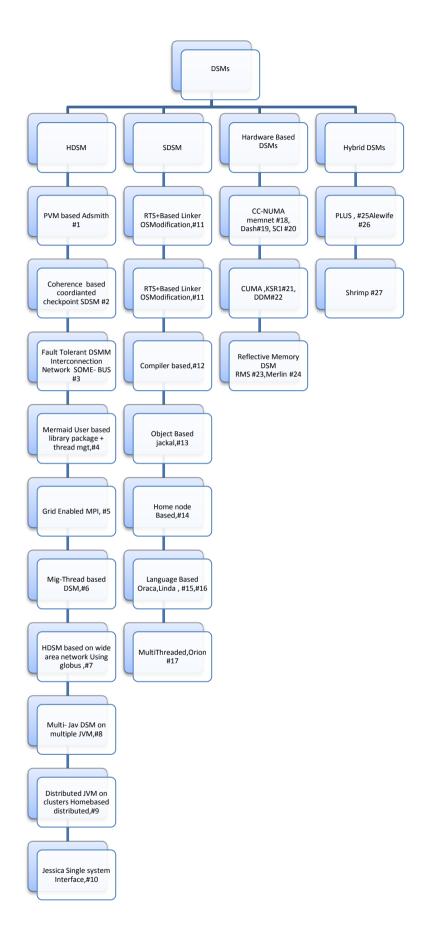

| Figure 1.2 | DSM taxonomy                                                | 5   |

| Figure 1.3 | HDSM taxonomy                                               | 8   |

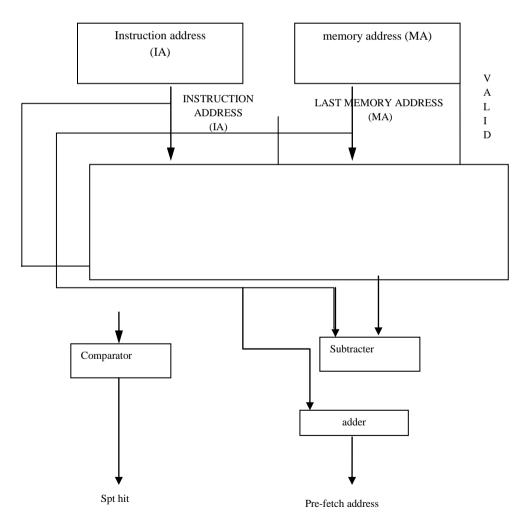

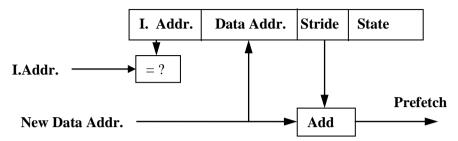

| Figure 2.1 | Stride Prediction Table                                     | 43  |

| Figure 2.2 | I detection scheme(RPT)                                     | 46  |

| Figure 3.1 | Thread pool Executor diagram indicating corepoolsize        | 58  |

|            | and maxpoolsize                                             |     |

| Figure 3.2 | Matrix Multiplication Performance                           | 76  |

| Figure 3.3 | N-queens Performance                                        | 77  |

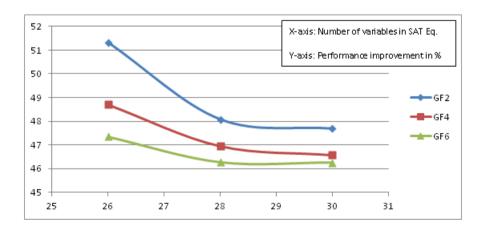

| Figure 3.4 | Satisfiability Performance for 2,4 and 6 CPUs               | 78  |

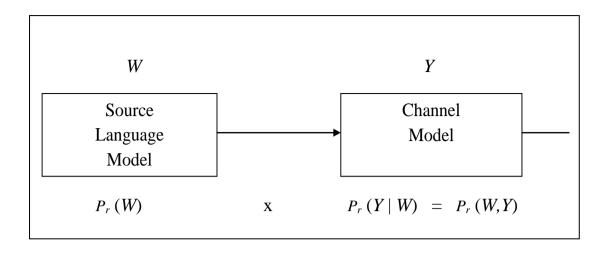

| Figure 4.1 | Source-channel setup                                        | 88  |

| Figure 4.2 | 1-gram representation for the above stride sequence         | 92  |

| Figure 4.3 | 2-gram representation for the above stride sequence         | 93  |

| Figure 4.4 | Stride lists along with conditional probabilities for grams | 98  |

|            | 1 to 10                                                     |     |

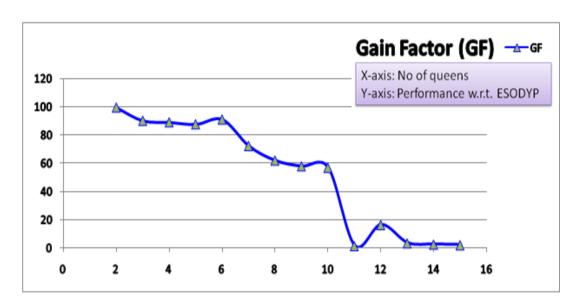

| Figure 4.5 | N-queens Gain Factor w.r.t. ESODYP                          | 103 |

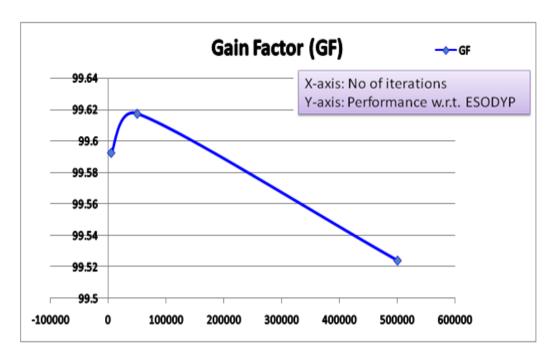

| Figure 4.6 | Performance Gain factor for Devil                           | 105 |

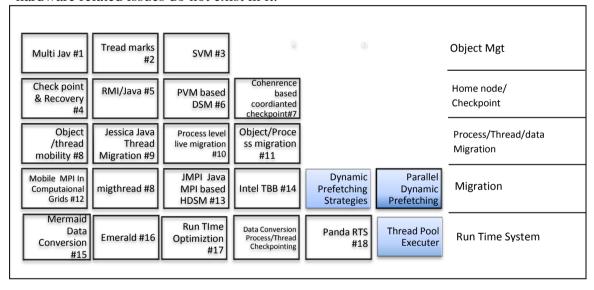

| Figure 6.1 | Proposed Heterogeneous Distributed Shared Memories          | 125 |

|            | Architectural Framework                                     |     |

# **List of Tables**

| Table 3.1 | Matrix Multiplication with varying matrix size and varying CPUs.                 | 76  |

|-----------|----------------------------------------------------------------------------------|-----|

| Table 3.2 | Nqueens Problem with varying CPUS and varying corePoolSize                       | 77  |

| Table 3.3 | Boolean Satisfiability Problem with varying cpus and varying number of equations | 78  |

| Table 4.1 | N-Queens problem performance with ESODYP and n-gram                              | 102 |

| Table 4.2 | Execution time Summary Table for Application DEVIL both ESODYP and n-gram        | 104 |

| Table 5.1 | Index of the stride stored in array                                              | 112 |

| Table 5.2 | One Entry stride                                                                 | 113 |

| Table 5.3 | Index entries for 2,16 stride sequence                                           | 114 |

| Table 5.4 | Index entries for 2, 32 stride sequence                                          | 114 |

| Table 5.5 | Index entries for 4, 9 & 9, 25 stride sequences                                  | 114 |

| Table 5.6 | Sorted Stride Sequences                                                          | 115 |

| Table 5.7 | Sorted Stride Sequences                                                          | 115 |

| Table 5.8 | Entry formed by process id 1                                                     | 117 |

| Table 5.9 | Entries are formed by process id 2                                               | 117 |

| Table 5.10 Entries are formed by process id 2                                            | 118 |

|------------------------------------------------------------------------------------------|-----|

| Table 5.11 Entries are formed by process id 2                                            | 118 |

| Table 5.12 Entries are formed by process id 2                                            | 119 |

| Table 5.13 2-gram stridelist with count and conditional probability                      | 120 |

| Table 5.14 stride list for 3-gram to 6-gram along with count and conditional probability | 122 |

#### **List of Publications**

- Sitharamaiah Ramisetti, Rajeev Wankar, Design of Hierarchical Thread Pool Executor for DSM, 2011 Second International Conference on Intelligent Systems, Modeling and Simulation (ISMS2011), Kaula Lumpur, Phnompeng Combodia, January24-28,2011,PP: 284-288.

- 2. Sitharamaiah Ramisetti, Rajeev Wankar, C.R.Rao, Design of n-gram based Dynamic Pre-fetching for DSM, International Conference on Algorithms and Parallel Processing, September 4-7, Fukuoka, Japan ICA3PP 2012, Part II, LNCS 7440, pp. 217–224, 2012.

- 3. Sitharamaiah Ramisetti, Rajeev Wankar, Parallel algorithm for n-gram based Dynamic Pre-fetching for DSM. (Ready for the communication).

- 4. Sitharamaiah Ramisetti, Rajeev Wankar, Component architecture and design issues in HDSM. (Ready for the communication).

#### **Abstract**

In the last two decades or so, many researchers paid lot of attention to several aspects of Distributed Shared Memory systems (DSM) varying from theoretical design to implementation of several components. To the best of our knowledge no one has proposed any Unified integrated framework for Heterogeneous DSM. This thesis proposes an integrated abstract framework for HDSM. Several components of it are pluggable/user selectable, which when integrated can become operational and realizable. It has two important components Hierarchical Thread Pool Executer and Dynamic Pre-fetching strategies and its parallelization, which are important contributions of this thesis.

Thread Pool Executor (TPE) is a software component which facilitates the assignment of incoming requests in the form of tasks to the worker threads. General philosophy used in TPE is to discourage more tasks. If still more tasks are arrived TPE throws exception and tasks are rejected. Thread pool executor is an essential component of every DSM and majority of the DSM suffers with this drawback of TPE design.

If we would like to overcome these limitations, we need to have a TPE which is scalable, efficient, and instead of raising exceptions should be able to accept request and migrate it other systems (nodes). *The proposed Hierarchical Thread pool Executor (HTPE)* has several features which will take into account the parameters of the underlying operating system, hardware and dynamic load of nodes to arrive at a thread migration mechanism to exploit and use resources. Several application programs are tested with this proposed HTPE and significant speedup/performance improvement is observed and reported.

Many earlier reported works have shown that data pre-fetching can be an efficient answer to the well-known memory stalls. If one can reduce these stalls, it leads to performance improvement in terms of overall execution time of a given application. In this thesis we propose a new n-gram model based dynamic pre-fetching strategy for prediction, which is based on the concept that if we compute conditional probabilities of the stride sequences of previous n steps and predict the most probable stride. Here

n is an integer which indicates number of grams. The strides that are already prefetched are preserved so that we can ignore them if the same stride number is referenced by the program due to principle of locality of reference with the fact that it is available in the memory, hence we need not pre-fetch it. The model also gives the best probable and least probable stride sequences, this information can further be used for dynamic prediction. Experimental results show that the proposed model is far efficient and presents user certain additional input about the behavior of the application. The model flushes once number of miss-predictions exceed predetermined limit. One can improve the performance of the existing compiler based Software Distributed Shared Memory (SDSM) systems using this model. Several application programs are tested with this proposed Dynamic Pre-fetcher and significant speedup/performance improvement is observed and reported.

The sequential dynamic pre-fetcher discussed above works on each node of the DSM. Since nodes of DSM can be muticore/multiprocessor, it is appropriate to propose a parallel method that can take advantage of this kind of architecture.

Looking into sequential counterpart it can be observed that the process also involves inherent parallelism for computing the stride sequences. Also it was felt that the process of learning phase of the model, where in model remembers the strides being referred can be optimized. Since the parallelism is available at finer level, the most appropriate theoretical model for parallel computation is PRAM model. The parallel algorithm based on this model is presented that shows a theoretical speedup and presented in the thesis.

#### **Chapter 1. Introduction**

#### 1.1 Introduction

Over the last two decades many researchers have designed and implemented several categories of Distributed Shared Memory (DSM) or Heterogeneous DSM (HDSM), but to the best of our knowledge no one has proposed a generalized framework for HDSM which covers all the aspects of them. This thesis does not advocate to use any particular implementation or technology for HDSM, but proposes a generalize framework of HDSM from our perspective, and improve the efficiency of few essential components of any DSM/HDSM. It is suggested that if we take these component and plug-in software modules, we can build a reasonable HDSM. Through the journey of this component development, we realized that further study of some of the components like Hierarchical Thread Pool Executor (HTPE) and Prefetching strategies are very important and there is ample scope to improve overall performance (compare to the existing components available in the literature) if they are designed carefully. In this thesis, we propose efficient theoretical design and practical implementations of these two components. The work presented in this thesis is in the larger context of DSM, more specifically with reference to the Heterogeneity in it.

A shared memory system will have main memory created by combining the main memories of all the participating processors, and it is shared by all the processors. This architecture is termed as tightly coupled multi-processors system. Since the memory is common to all the processors, any processor can access any part of the memory. The scalability of such a system is limited by the amount of memory available presently and the maximum memory addressable by the any of the processors.

Shared Memory model is in general a convenient programming model with simple data sharing through a uniform method of reading and writing. The memory is connected to the processors through a shared bus. As a result it suffers from increased

contention and longer latencies in accessing the memory. The contention is due to the fact that the same memory location may be accessed by more than one processor and several processors have to access the memory through the shared bus. Since the bus can be accessed by only one processor at one time, inherent delay occurs in waiting for the bus to get free for further access by any other processor.

Though Shared Memory processing model is popular in parallel programming environment apart from the issues discussed in the last paragraph, it has its limitations: address space provided by the manufacturer and contention for memory. If the application program requires large memory that cannot be supported by the shared memory processor, then we need to divide the problem into several segments and implement the problem on two or more systems. An obvious choice for this problem is, if we are able to provide a single logical address space to the user then the application programmer can develop application logic and execute her/his program on the set of machines that provide the facility. This has further lead to the evolution and realization of DSMs.

#### 1.2 Distributed Shared Memory

A DSM [99] system logically implements the shared memory model on a physically distributed memory system. The DSM system hides remote communication mechanism from the application writer, preserving the programming ease and portability typical of shared memory systems. DSM systems allow relatively easy modification and efficient execution of existing shared memory system applications, which preserves software investments while maximizing the resulting performance.

Figure 1.1 A representative diagram showing DSM

A distributed shared memory system (DSM) consists of multiple independent processing nodes with local memory modules, connected by interconnection network, providing a logical address space for all processors. The interconnection network provides the necessary communication abstraction required for the application to run seamlessly. This will alleviate the difficulty of a large program which requires considerable memory, which hitherto cannot be provided by single computer system.

Advantages offered by DSM are ease of programming; portability achieved through shared memory programming paradigm, low cost, better scalability and being free from hardware bottlenecks. The DSM provides an unbounded logical address space for the user application. As a result, the user application need not be aware of implementation details and can focus only on the application rather than spending time in looking at the runtime errors emanating from implementation issues of the underlying hardware and software.

To achieve the ease of programming, cost-effectiveness and scalability, DSM systems logically implement the shared memory model on physically distributed memories. System designers can resort to the specific mechanism in realizing the shared-memory abstraction in hardware or software in different ways. The DSM system abstracts (hides) remote communication mechanisms from application developer, preserving the programming ease and portability that is typical of shared memory systems.

The Distributed Shared Memory systems are classified into three categories: Software Distributed Shared Memory (SDSM), Hardware Distributed Shared Memory and Hybrid Distributed Shared Memory.

The Distributed Shared Memory systems are also classified into: Homogeneous Distributed Shared memory and Heterogeneous Shared Memory. Unless otherwise stated, the DSMs are considered as homogeneous DSMS. The classification is based on the hardware platforms that are chosen for implementing the DSM. If they are non-uniform it is called heterogeneous or if same hardware systems are used for realization, we call this as homogenous DSMs.

Figure 1.2 DSM taxonomy

#### 1.2.1 DSM taxonomy references:

- #1. Ce-Kuen Shieh, An-Chow Lai, Jyh-Chang Ueng, Tyng-Yue Liang, Tzu-Chiang Chang, Su-Cheong Mac, Cohesion: an efficient distributed shared memory system supporting multiple memory consistency models. *PAS '95 Proceedings of the First Aizu International Symposium on Parallel Algorithms/Architecture Synthesis*, pp: 146-152, 1995.

- #2. Angkul Kongmunvattana, Santipong Tanchatchawal, Nian-Feng Tzeng, Coherence-Based Coordinated Checkpointing for Software Distributed SharedMemory Systems. *ICDCS '00 Proceedings of the The 20th International Conference on Distributed Computing Systems (ICDCS 2000)*, pp. 556, 2000.

- #3. Diana Hecht, Constantine Katsinis, Fault-tolerant Distributed-Shared-Memory on a Broadcast-based Interconnection Network. *Parallel and Distributed Processing*, Volume: 1800, pp: 1286-1290, 2000.

- #4. Songnian Zhou, Michael Stumm, Tim McInerney, Extending Distributed Shared Memory to Heterogeneous Environments, *10th International Conference on Distributed Computing Systems*, pp. 30-37, 1990.

- #5. Ian Foster, Nicholas T. Karonis, A grid-enabled MPI: message passing in heterogeneous distributed computing systems. *Supercomputing '98 Proceedings of the 1998 ACM/IEEE conference on Supercomputing*, pp: 1-11, 1998.

- #6. Hai Jiang; Chaudhary, V., MigThread: thread migration in DSM systems. *International Conference on Parallel Processing Workshops*, pp:581-588, 2002.

- #7. Weisong Shi, Heterogeneous Distributed Shared Memory on Wide Area Network. *IEEE TCCA Newsletter*, pp: 71–80, 2001.

- #8. X. Chen, V. H. Allan, MultiJav: A Distributed Shared Memory System Based on Multiple Java Virtual Machines. *In Proceedings of the Conference on Parallel and Distributed Processing Techniques and Applications*, pp. 91-98, 1998.

- #9. Matchy J.M. Ma, Cho-Li Wang, Francis C.M. Lau, JESSICA: Java-Enabled Single-System-Image Computing Architecture. *Journal of Parallel and Distributed Computing*, Volume: 60, Issue: 10, pp: 1194–1222, October 2000.

- #10. Wenzhang Zhu, Cho-Li Wang, Lau, F.C.M., JESSICA2: a distributed Java Virtual Machine with transparent thread migration support. *IEEE International Conference on Cluster Computing*, pp: 381-388, 2002.

- #11. Bennett J. K., J. B. Carter J. B., W. Zwaenepoel, Munin: distributed shared memory based on type-specific memory coherence. *PPOPP '90 Proceedings of the second ACM SIGPLAN symposium on Principles & practice of parallel programming*, ACM New York, NY, USA, Volume: 25, Issue: 3, pp: 168-176, March 1990.

- #12. Cristiana Amza, Alan L. Cox, Sandhya Dwarkadas, Pete Keleher, Honghui Lu, Ramakrishnan Rajamony, Weimin Yu, Willy Zwaenepoel, TreadMarks: shared memory computing on networks of workstations. *Journal Computer*, Volume: 29, Issue: 2, pp: 18-28, February 1996.

- #13. R.veldema,R.A.F.Bhoedjang,H.E.Bal Jackal, A Compiler Based Implementation of Java for Clusters Of Workstations (2001). *In proceedings of Principles & practice of parallel programming PPOP*, 2001.

- #14. Weiwu Hu, Weisong Shi, Zhimin Tang, JIAJIA: A software DSM system based on a new cache coherence protocol. *High-Performance Computing and Networking, LNCS*, Volume: 1593, pp: 461-472, 1999.

- #15. Henri E. Bal, Orca: a language for distributed programming. *ACM SIGPLAN*, Volume: 25, Issue: 5, pp: 17-24, May 1990.

- #16. Nicholas Carriero, David Gelernter, Linda in context. *Communications of the ACM*, Volume: 32, Issue: 4, pp: 444-458, April 1989.

- #17. Ng M. C., Wong W. F., ORION: an dynamic home-based software distributed shared memory system. *Proceedings of the Seventh International Conference on Parallel and Distributed Systems*, pp. 187, 2000.

- #18. Delp, G.S., Farber, D.J., Minnich, R.G., Smith, J.M., Tam, M.C., Memory as a network abstraction, *Network, IEEE*, Volume: 5, Issue: 4, pp: 34-41, July 1991.

- #19. James, D.V., The Scalable Coherent Interface: scaling to high-performance systems. *Digest of Papers Compcon Spring '94*, pp.64-71, February March 1994.

- #20. Daniel Lenoski, Kourosh Gharachorloo, James Laudon J., Anoop Gupta, Hennessy J., Mark Horowitz, Monica Lam, Design of Scalable Shared-Memory Multiprocessors: The DASH Approach. *Compcon Spring '90. Intellect*, pp. 62-67, 1990.

- #21. S. Frank, J.Burkardt III, J.Rothnie, The KSR1: Bridging the Gap between Shared Memory and MPPs" Compcon Sping '93, pp. 285-294.,march 1993.

- #22. E. Hagersten, K. Landin, and S. Haridi, "DDM-A Cache-Only Memory Architecture," IEEE Computer, Vol. 25, No.9, pp. 44-54, Sept. 1992.

- #23. Iftode, L., Singh, J. P., Li, K., Scope Consistency: A Bridge between Release Consistency and Entry Consistency. *Theory of Computing Systems*, Volume: 31, Issue: 4, pp: 451-473, August 1998.

- #24. Maples, Creve, Wittie, L., MERLIN. A superglue for multicomputer systems. Compcon Spring '90, Intellectual Leverage. Digest of Papers, Thirty-Fifth IEEE Computer Society International Conference, pp. 73-81, 1990.

- #25. Robert Bisiani, Mosur Ravishankar, PLUS: A distributed shared-memory system. *17th Annual International Symposium on Computer Architecture*, pp: 115-124, May 1990.

- #26. Anant Agarwal, David Chaiken, David Kranz, John Kubiatowicz, Kiyoshi Kurihara, Gino Maa, Dan Nussbaum, Mike Parkin, Donald Yeung, The MIT Alewife Machine: A Large-Scale Distributed-Memory Multiprocessor *In Proceedings of Workshop on Scalable Shared Memory Multiprocessors*, 1991.

- #27. Sun Microsystems, Inc., External Data Representation Standard: Protocol Specification. *RFC1014 by the ARPA Network Information Center*.

#### 1.3 Heterogeneous Distributed Shared Memory

The Heterogeneous Distributed Shared Memory Systems (HDSMs) are systems that allow different hardware platforms. This is relatively more complex and implementation dependent as the way data is stored and the instruction set and hardware environment is used. Operating systems themselves pose several issues that need to be addressed in realizing HDSM. The other important aspect of HDSM is *process migration* due to the fact that the hardware of the other node, where the process needs to run is not same and the special mechanism of migration needs to take

place. In case of homogeneous SDSM, it is easy to get process to be migrated as the hardware related issues do not exist in it.

Figure 1.3 HDSM taxonomy

#### 1.3.1 HDSM taxonomy references:

- #1. X. Chen, V. H. Allan, MultiJav: A Distributed Shared Memory System Based on Multiple Java Virtual Machines. *In Proceedings of the Conference on Parallel and Distributed Processing Techniques and Applications*, pp. 91-98, 1998.

- #2. Cristiana Amza, Alan L. Cox, Sandhya Dwarkadas, Pete Keleher, Honghui Lu, Ramakrishnan Rajamony, Weimin Yu, Willy Zwaenepoel, TreadMarks: shared memory computing on networks of workstations. *Journal Computer*, Volume: 29, Issue: 2, pp: 18-28, February 1996.

- #3. Songnian Zhou, Michael Stumm, Tim McInerney, Extending Distributed Shared Memory to Heterogeneous Environments, *10th International Conference on Distributed Computing Systems*, pp. 30-37, 1990.

- #4. Balkrishna Ramkumar, Volker Strumpen, Portable Checkpointing for Heterogeneous Architecturesm. FTCS '97 Proceedings of the 27th International Symposium on Fault-Tolerant Computing (FTCS '97), pp. 58, 1997.

- #5. Jason Maassen, Thilo Kielmann, Henri E. Bal, Efficient replicated method invocation in Java. *JAVA '00 Proceedings of the ACM 2000 conference on Java Grande*, pp: 88-96, 2000.

- #6. Jack J. Dongarra, G. A. Geist, Robert Manchek, V. S. Sunderam, Integrated PVM Framework Supports Heterogeneous Network Computing. *Computers in Physics*, pp: 166-175, 1993.

- #7. Angkul Kongmunvattana, Santipong Tanchatchawal, Nian-Feng Tzeng, Coherence-Based Coordinated Checkpointing for Software Distributed SharedMemory Systems. *ICDCS '00 Proceedings of the The 20th International Conference on Distributed Computing Systems (ICDCS 2000)*, pp. 556, 2000.

- #8. Ian Foster, Nicholas T. Karonis, A grid-enabled MPI: message passing in heterogeneous distributed computing systems. *Supercomputing '98 Proceedings of the 1998 ACM/IEEE conference on Supercomputing*, pp. 1-11, 1998.

- #9. Matchy J.M. Ma, Cho-Li Wang, Francis C.M. Lau, JESSICA: Java-Enabled Single-System-Image Computing Architecture. *Journal of Parallel and Distributed Computing*, Volume: 60, Issue: 10, pp: 1194–1222, October 2000.

- #10. Dejan S. Miloji, Fred Douglis, Yves Paindaveine, Richard Wheeler, Songnian Zhou, Eleanor Rieffel, Wolfgang Polak, Process migration. *ACM Computing Surveys*, Volume: 32, Issue: 3, pp: 241—299, September 2000.

- #11. Mark Nuttall, Brief survey of systems providing process or object migration facilities. *ACM SIGOPS Operating Systems*, Volume: 28 Issue: 4, pp: 64-80, October 1994.

- #12. Ian Foster, Nicholas T. Karonis, A grid-enabled MPI: message passing in heterogeneous distributed computing systems. *Supercomputing '98 Proceedings of the 1998 ACM/IEEE conference on Supercomputing*, pp. 1-11, 1998.

- #13. Kivanc Dincer, jmpi and a Performance Instrumentation Analysis and Visualization Tool for jmpi, *First UK Workshop on Java for High Performance Network Computing*, EUROPAR-98, Southampton, UK, September 2-3, 1998.

- #14. Wooyoung Kim and Michael Voss, Multi-core Desktop Programming with Intel TBB, IEEE *Software* ,pp:23-31,January/February 2011.

- #15. Daniel J. S., Kourosh Gharachorloo, Design and performance of the Shasta distributed shared memory protocol. *ICS '97 Proceedings of the 11th international conference on Supercomputing*, ACM New York, NY, USA, pp: 245-252, 1997.

#16. Jul, E., Steensgaard, B., Implementation of distributed objects in Emerald. *International Workshop on Object Orientation in Operating Systems*, pp. 130-132, Oct 1991.

#17. R. Veldema, R. F. H. Hofman, R. A. F. Bhoedjang, C.J.H. Jacobs, H. E. Bal, Source Level Global Optimizations for Fine-Grain Distributed Shared Memory Systems. *ACM SIGPLAN symposium on Principles and practices of parallel programming*, *PoPP '01*, Volume: 36, Issue: 7, pp: 83-92, 2001.

#18. Raoul Bhoedjang, Tim Ruhl, Rutger Hofman, Koen Langendoen, Henri Bal, Frans Kaashoek, Panda: a portable platform to support parallel programming languages. *Sedms'93 USENIX Systems on USENIX Experiences with Distributed and Multiprocessor Systems*, Volume: 4, pp: 11-11, 1993.

#### 1.4 Motivation and Objective

The earlier concentration of research was focused mainly on implementation aspects and interoperability of different systems [41], [43], [47], [48]. To the best of our knowledge, no one has proposed any prototype of integrated system nor did they propose any learning based techniques to speed up the processing of components of DSM. This motivated us to design and implement superior components like Hierarchical Thread Pool Executor and Dynamic Pre-fetching Strategies and its parallelization in this work, and show how they fit into our proposed framework for HDSM.

As part of the research, we have proposed a novel integrated frame work for HDSM. The objective of integrated framework is to identify various component and later required methods of implementation, and to propose a solution for realization and integration of components of it.

We have identified that Thread Pool executor is one of the major component of any DSM implementation. The present thread pool executor is based on the usage of work stealing algorithm [102] and using JMM framework [103]. Some of the proposed modifications to the work stealing can be seen in [104]. Despite these techniques, it does not address some crucial issues like thread blocking.

We have proposed a new Hierarchical Thread Pool Executor which uses non-blocking queues. The incoming requests (tasks) are stored in non-blocking queue which are sorted on priority. An efficient thread migration mechanism based on min-heap system hierarchy is proposed. If the Thread Pool Executor (TPE) has more worker threads than corePoolSize then the thread migration is initiated which will place the thread on the other system with minimal load. We have integrated this HTPE with standard applications for both performance improvement and implementation, and found that it gives better performance on benchmark programs.

Another very important component of DSM is pre-fetching strategies component. Pre-fetching of objects in DSM will make the object available in cache before it is accessed. One of the classical techniques proposed in the literature is a dynamic software model based pre-fetcher [86]. This will keep track of the objects present in memory and identifies most probable objects and pre-fetches these objects to be later used by the DSM. This technique which is called An Entirely Software and Dynamic Data Pre-fetcher (ESODYP) is based on Markov model.

In this work we propose an *n-gram* model based dynamic Pre-fetcher that cleverly uses the past pre-fetching history to pre-fetch next probable sequences of pages/objects. This newly proposed technique outperforms ESODYP on several benchmark programs we tested. To the best of our knowledge, the use of *n-gram* model for pre-fetching has not been used in DSM's in the past.

Although the proposed dynamic pre-fetcher is sequential in nature, we observed the inherent parallelism in the computation if we change certain parameters without affecting the outcome. This encouraged us to propose a theoretical parallel algorithm of the dynamic pre-fetcher, which is based on the PRAM model-based parallelization which is theoretically superior compare to the sequential counterpart in terms for time.

#### 1.5 Research Problems Related to Objectives

#### 1.5.1 HDSM Framework

Though HDSMs are implemented by different researchers, each of these implementations differs from one another and no commonality exists. We are proposing a layered framework which will be able to visualize and configure various

pluggable modules required for HDSM. The proposed HDSM framework consists of Application Layer, Object Management Layer, Migration and Consistency Layer and Multi-core Operation Layer.

Application layer is the one with which the user interacts with the HDSM system. Object Management Layer deals with the Object Management (creating an object, grouping and managing), which partitions the shared memory according to logical data structures.

Migration and Consistency Layer comprises of two sub layers. Consistency sub layer with Home node Management and checkpoint & restart. Migration sub layer consists of data migration, process migration and Thread migration. Home node Management deals with consistency and data integrity.

Multi-core Operations Layer has two sub layers namely Run Time System Layer and Interface Layer for the Multi-core. The Run Time System (RTS) Layer forms the implementation dependent actions required to be executed at the machine level. Interface Layer for the Multi-core has Network Library, Thread Pool Executor, Dynamic Pre-fetching Strategies, Garbage Collector and multi-Threaded library are modules that will be operational as per the requirement of a user application.

Finally the Operating System and Hardware Layer deals with operating system services which manages hardware and various system services provided by the operating system .The detailed description of framework for HDSM is done in Chapter 6.

#### **1.5.2 Hierarchical Thread Pool Executor (HTPE)**

In several DSMs, threads are integral part of DSM implementation (ex: object based DSM) and managing their life cycle is an important issue. The straight forward approach for building a thread based application is to create a new thread each time a request arrives and service the request in the new thread. Instead of creating and invoking a thread every time one can design for a thread pool. A thread pool executor provides a pool of worker threads which will enhance the execution of DSM. We have proposed and implemented a novel hierarchical thread pool executor which will enhance the performance of DSM which uses non-blocking queues (containing ready

threads sorted on priority) and priority principles. This is dealt in detail in Chapter 3 of the thesis.

#### 1.5.3 Dynamic Pre-fetching Strategies:

Pre-fetching is a mechanism that will make the required datum in cache memory before it is used by the processor. This avoids memory stalls which take several milleseconds to bring required datum into main memory. The proposed dynamic prefetching is an entirely software n-gram based model pre-fetching technique. The n-gram model predicts the next accessible stride (a range of addresses analogous to page in operating system terminology) and this is integrated into the DSM modules.

Dynamic pre-fetching exploits the locality of reference by the DSM modules. The locality of reference (for DSM module) says, "When an application program module is executed on one of the nodes of DSM, the execution is confined for a small period of time around a sequence of instructions (ex: a for loop being executed by a JAVA method)". The pre-fetching speeds up overall execution of this module as the related strides are available in processor cache due to the fact that the strides are pre-fetched ahead and are available in advance before these are referenced by the module repeatedly due to locality of reference.

This is dealt in detail in Chapter 4 of the thesis.

#### 1.5.4 Parallelization of n-gram Model

We propose a novel parallel n-gram model, which theoretically gives better performance in terms of the parallel time compared to its sequential counterpart. For exploiting the multiple read and random access of the data structure, we use array representations. The space is not a costly matter as only n number of pages will be in the main memory of the home node at any given snapshot of the program execution.

Looking into its sequential counterpart, it can be observed that the process of n-gram involves inherent parallelism. Moreover if we are working on a DSM system and many processors are available, the immediate extension of sequential pre-fetching to parallel pre-fetching and can be realized, especially if the nodes of DSM's are

multicores. Since the inherent parallelism is available at finer level of the sequential algorithm, the most appropriate theoretical model for parallel computation is Parallel Random Access Machine Model (PRAM). The parallel algorithm, its implementation of various programs, parallel time and the processor's complexity all are explained in Chapter 5 of the thesis.

#### 1.6 Research Contributions

- Sitaramaiah Ramisetti, Rajeev Wankar, Design of Hierarchical Thread Pool Executor for DSM, 2011 Second International Conference on Intelligent Systems, Modelling and Simulation, pages: 284-288, January 2011. (Scopus Indexed)

- 2. Sitaramaiah Ramisetti, Rajeev Wankar, C.R.Rao, Design of n-gram based Dynamic Pre-fetching for DSM, International Conference on Algorithms and Parallel Processing ICA3PP-2012, September 4-7, 2012. (DBLP Indexed)

- 3. Sitaramaiah Ramisetti, Rajeev Wankar, Parallel algorithm for n-gram based dynamic Pre-fetching for DSM. (Ready for Communication).

- 4. Sitaramaiah Ramisetti, Rajeev Wankar, Component architecture and design issues in HDSM. (Ready for Communication).

#### 1.7 Organization of Thesis

Our work is organized in to 7 chapters. The details are as given below:

- Chapter 1 covers Introduction to the Heterogeneous Distributed shared memory and motivation for our research.

- Chapter 2 covers extensive literature survey and review of research being carried out in the area of HDSM.

Chapter 3 deals with the proposed Hierarchical Thread Pool Executor for DSM.

Chapter 4 covers in detail the n-gram model based Dynamic Pre-fetching strategies for DSM.

Chapter 5 covers the parallelization of n-gram model and algorithm.

Chapter 6 refers to the proposed component based Heterogeneous Distributed Shared Memory architectural framework.

Chapter 7 covers the conclusion and future work.

### **Chapter 2. Literature Survey**

#### 2.1 Distributed Shared Memory Systems

In the last two decades or so, several researchers paid lot of attention to several aspects of DSM varying from theoretical design to implementation of several components. In this Chapter, we provide brief description of work done by them. The survey concentrates basically on the proposed techniques presented in this thesis.

#### 2.1.1 Software Distributed Shared Memory

IVY [10] is a shared virtual memory system which provides virtual address space shared among all processors in loosely coupled multi-processors. Such a memory can solve many problems in message passing systems on loosely coupled multi-processor and is realized using an Apollo ring network. The experiments with prototype show that parallel programs using a shared virtual memory yield linear speedups. IVY consists of 5 modules namely Initialization, remote operation, memory mapping, memory allocation and process management.

A user mode prototype is implemented on Apollo Domain, an integrated system of work stations and server computers connected by a 12 Mbit /Sec base band, single token ring network. IVY is implemented on top of modified operating system Aegies of Domain environment. The implementation is not particularly efficient but is simple and tractable.

**Munin** [9] is a DSM system that allows programs written for shared memory multiprocessors to be executed efficiently on distributed memory machines. Munin attempts to overcome the architectural limitations of shared memory machines, while maintaining their advantages in terms of ease of programming. The core of Munin is the runtime library that contains the fault handling, thread support, synchronization and other runtime mechanisms.

Munin supports four consistency protocols conventional, read\_only, migratory and w\_shared plus a suite of synchronization protocols for locks, barriers and condition

variables. In addition to the consistency protocols provided, Munin has a capability for users to install User written fault handlers and use them. Munin also has a facility for users to create consistency protocols of their own.

Each Munin node interacts with the V kernel to communicate with the other Munin nodes over the Ethernet and to manipulate the virtual memory system as part of maintaining the consistency of shared memory. Each node of an executing Munin program consists of a collection of Munin runtime threads that handle consistency and synchronization operations and one or more user threads performing the parallel computation. Munin programmers write parallel programs using threads as they would on a uniprocessor or a shared memory multiprocessor.

Although the Munin prototype was implemented on the V system (V-kernel), it could be made to run on any operating system that allows user programs to manipulate its own virtual memory mappings to handle page faults at user level, create and destroy processes on remote nodes exchange messages with remote processes and access uniprocessor synchronization support P and V.

Munin is unique in its use of loosely coherent memory, based on the partial order specified by a shared memory parallel program, and in its use of type-specific memory coherence. Instead of a single memory coherence mechanism for all shared data objects, Munin employs different mechanisms, each appropriate for a different class of shared data object. These type-specific mechanisms are part of a runtime system that accepts hints from the user or the compiler to determine the coherence mechanism to be used for each object.

Adaptive Software Cache Management for Distributed Shared Memory Architectures: Discusses an adaptive cache coherence mechanism that exploits semantic information about the expected or observed access behavior of particular data objects [27]. Munin employs several different mechanisms, each appropriate for a different category of shared data object, the technique of providing multiple coherence mechanisms is called as adaptivecaching. Adaptivecaching maintains coherence based on the expected or observed access behavior of each shared object and on the size of cached items.

PLUS[29] is a multiprocessor architecture tailored to the fast execution of a single multithreaded process. Its goal is to accelerate the execution of CPU-bound applications. PLUS support both shared memory and efficient synchronization. Memory access latency is reduced by non-demand replication of pages with hardware-supported coherence between replicated pages. The architecture has been simulated in detail, and some of the key measurements that have been used to substantiate the architectural decisions are presented. PLUS was aimed at efficiently executing a single multithreaded process by using distributed memories, hardware supported memory coherence and synchronization mechanisms.

The implementation of PLUS uses a general purpose Motorola 88000 processor (25MHz) with 32 Kbytes of cache and 8 or 32 Mbytes of main memory at each node. The memory was organized in two interleaved banks to sustain the burst bandwidth needed for cache line accesses. Global memory mapping, coherence management and atomic operations were performed by a hardware module that is implemented with Xilinx PLD's and PAL'S. In this implementation, each node can have up to 8 writes and 8 delayed operations in progress. The interconnection network uses a mesh router designed at Caltech. Each router has five pairs of *U0* links: one for the processor and one for each of its mesh neighbors. Links operate at 20 Mbyte in each direction. **SCSI** devices, audio peripherals and host computers can be attached to each node. Caching and issues such as address space structure and page replacement schemes were used to define taxonomy.

A taxonomy-based comparison of several distributed shared memory systems is given in [49]. Based on the taxonomy, three DSM efforts were examined in detail, namely: IVY, Clouds and MemNet.

CRL: high-performance all-software distributed shared memory [19]:The C/Region Library (CRL) is an all-software distributed shared memory (DSM) system. CRL requires no special compiler, hardware, or operating system support beyond the ability to send and receive messages. It provides a simple, portable, region-based shared address space programming model that is capable of delivering good performance on a wide range of multiprocessor and distributed system architectures.

Parallel applications built on top of CRL share data through regions. Each region is an arbitrarily sized contiguous area of memory. The programmer defines regions and delimits accesses to them using annotations. Regions are cached in the local memories of processors; cached copies are kept consistent using a directory-based coherence protocol. CRL achieves speedups better than that of those provided by Alewife's native support for shared memory, even for challenging applications (e.g., Barnes-Hut) and small problem sizes.

Distributed Shared Memory: Where We Are and Where We Should Be Headed [20]. This work reflects on: what have been the major advances in the area, what the important outstanding problems are, and what work needs to be done. Finally, it also reflects on a modest step towards solving these problems, namely the Quarks DSM system. The umbrella of the Computer Systems Laboratory at Utah has developed a distributed shared system named Quarks3. Quarks consists of a user-level library and associated header files that support DSM on collections of workstations. Quarks was built on SunOS 4.1, HP BSD 4.3, and HPUX; native Mach and IRIX 5.2. Quarks includes a number of modern DSM features such as support for multiple consistency protocols within an application on a per page basis (e.g., a write invalidate protocol providing strict consistency, a delayed write update protocol providing release consistency, etc.). An effort was made to make adding new protocols easy, allowing the research community to experiment with new protocols and compiler writers to develop specialized protocols.

Cohesion[51] is a prototype of DSM which supports two memory consistency models, namely Sequential consistency and Release consistency, within a single program to improve the performance and supports wide-variety of parallel programs for the system. Memory that is sequentially consistent is further divided into object-based and conventional (page-based) memory; where they are constructed in user-level and kernel-level, respectively. In object-based memory, the shared data is kept consistent at the granularity of an object; it is provided to improve the performance of the fine-grained parallel applications that may incur a significant overhead in conventional or release memory, as well as to eliminate unnecessary movement of the pages which are protected in a critical section.

On the other hand, the Release consistency model is supported in Cohesion to attack the problem of excessive network traffic and false sharing. Cohesion programs are written in C++, and the annotation of shared objects for release and object-based memory is accomplished by inheriting a system provided base class.

SCASH [2,3] is a software based DSM using PM (MPICH on PM using a cluster of systems employing myrinet switch) low-latency and high bandwidth communication library for a Myrinet gigabit network and memory management functions, such as memory protection, supported by an operating system kernel. It is implemented as a user level runtime library. To obtain high performance communication and support multi-user environments, it was co-designed PM and the run-time routine for a programming language. Several unique features, e.g., network context switching and a *Modified ACK/NACK* flow control algorithm, were provided for PM. This could be used as a platform for implementing SDSM or any other parallel applications.

MPC++ version2 Template library, called Multiple Threads Template Library (MTTL), supports local and remote thread invocation, synchronization structures and global pointers. The global pointers allow access to remote objects and its distribution to multiple processors. Such a facility is useful to implement data parallel applications in which processor's local memory is often distributed to other processors.

SCASH is a page based DSM, where consistency is maintained per page basis, utilizes Release Consistency model with multiple writer protocol. It also utilizes dynamic home node mechanism realized using concepts of diff and write invalidate and update and memory barrier synchronization mechanism.

The *Home* node of a page is the node that keeps the latest data of the page and the page directory which represents the set of nodes sharing the page. A node, intending to share a page, must copy the latest data of the page found on the *home* node. When the memory barrier synchronization is issued, nodes, having modified a shared page, must notify the home node of the difference between the former and the new page data. The home maintains the latest page data by applying all the differences received from those nodes.

The *base* is the node that knows the latest home node. All nodes know the base nodes of all pages. Even if a node does not know the home of a page, the home can be ascertained by asking the base node. Using **SCASH** home selection algorithm, the home node is moved to another node which has modified a large part of the page,

when and only when a home node does not write to the page and other nodes which share the page do write to the page. SCASH employs dynamic home node allocation.

An interesting work on Compiler and Software Distributed Shared Memory Support for Irregular Applications [8] was done by Honghui Lut, Alan L.Cox, Sandhya Dwarkadas. A modified version of TreadMarks[7] that supports prefetching and aggregation is used for analysis and performance measure of two irregular applications were carried in this work. They used another method used for comparison that use Parascope, parallel programming environment to carry out the required compiler analysis. The performance results for two irregular applications, moldyn (Moldyn is a molecular dynamics simulation) and nbf(NBF is the kernel of *a* molecular dynamics simulation) were compared.

Comparative evaluation of latency tolerance techniques for software distributed shared memory is proposed in [21]. A key challenge in achieving high performance on software DSMs is overcoming their relatively large communication latencies. Two techniques which address this problem: prefetching and multithreading. While previous studies have examined each of these techniques in isolation, in this work, these techniques were evaluated using a consistent hardware platform and set of applications, thereby allowing direct comparisons.

These were studied combining prefetching and multithreading in a software DSM and experiments on real hardware using a full implementation of both techniques. Experimental results demonstrate that both prefetching and multithreading result in significant performance improvements when applied individually. In addition, it was observed that prefetching and multithreading can potentially complement each other by using prefetching to hide memory latency and multithreading to hide synchronization latency.

JIAJIA [1] is a DSM based on Scope consistency and employing home node. The JIAJIA utilizes scope consistency and uses multiple writer protocol to update the data located in page. Each shared page has a fixed global address, which determines the home of the page. Initially, a page is mapped to its global address only by its home processor. The scope consistency used by JIAJIA gives better performance than lazy release consistency used by several other DSMs. The home nodes are maintained and the home node address is a global address space and is mapped using mmap() system

service. The referred address is first checked in the local home node. If it is not found, then the remote home pages are checked on other processor and it is acquired by using global address of the shared page. Reference to a non-home page causes the delivery of SIGSEGV signal. The SIGSEGV handler then maps the fault page to the global address of the page in local address space. JIAJIA uses fixed memory consistency model and fixed write propagation (write invalidate) strategy. Multiple write technique is used to reduce false sharing.

Since it uses scope consistency, global address space and page level mapping, the message passing is minimized which in turn gives better performance for applications such as TSP, Water and Barnes. JIAJIA can solve large problems that cannot be solved by other DSMs due to memory size limitation. JIAJIA gives better performance than CVM for many tested applications. This is one of the few home based DSM, hence gives better performance.

ORION [11] is multithreaded software distributed shared memory (DSM) system. It was developed to provide POSIX-thread (pthread) like interface. This will avoid creating another unique set of application programming interface and ease the porting of pthread programs to a distributed environment. Orion implements home-based Memory Release consistency model. It also employs two adaptive schemes for home-based DSM systems, namely home migration and dynamic adaptation between write-invalidation and write-update protocols.

An Orion program typically starts with a number of nodes or hosts specified by the user. Depending on the number of nodes specified, the master node that is ranked 0 remotely spawns the same program on other nodes and assigns them a different rank each. The Data Processing Interface(DPI) library undertakes the task of automatic remote process spawning during start up. DPI is a separate network communications library to provide the basic send, buffered send and receive functions found in MPI. Some group communication functions like barrier, all-gather and other functions are provided too.

Orion implements home-based eager release consistency (HERC) supporting the multiple writer, write-invalidate and write-update protocols. Typically in an Orion application, user codes interfaces with the Orion API, which in turn makes use of functions from pthread and *data passing interface*.

Implementation of a Software Distributed Shared Memory (DSM) over Virtual Interface Architecture (VIA) for a Linux-based cluster of PCs [17] is implemented and its performance evaluation is done. VIA is a user-level memory-mapped communication model that provides zero-copy communication and low-overhead by excluding the operating system kernel from the communication path. The VI architecture is composed of four basic components: Virtual Interfaces, Completion Queues, VI Providers, and VI Consumers. The DSM protocol implemented on VIA is Home-based Lazy Release Consistency (HLRC) that previous studies have shown to exhibit good scalability by reducing the number of messages and memory overhead compared to the homeless counterpart.

A Distributed Shared Memory (DSM) system provides a distributed application with a shared virtual address space. Choosing a memory consistency model is one of the main decisions in designing a DSM system. While Sequential Consistency provides a simple and intuitive programming model, relaxed consistency models allow memory accesses to be parallelized, improving runtime performance. The home-based lazy release consistency (HLRC) protocol was implemented such that it supports preemptive multithreading and compare its performance with the efficient multithreaded SC protocol in a comparison of sequential consistency with home-based lazy release consistency for software distributed shared memory.

The runtime performance of two memory coherence protocols [42] a multithreaded implementation of the HLRC model and an efficient multithreaded implementation of the SC model that uses a MultiView memory mapping technique were compared. Comparison was carried on the same test bed environment with benchmark suite and investigated the effectiveness and scalability of both these protocols. Three consistency protocols with four sizes of coherence granularity were tested: SC, single writer LRC, and HLRC. The results show that no single combination of protocol and granularity performs best for all the applications. A combination of the SC protocol and fine granularity performed well with 7 of the 12 applications.

Home migration is used to tackle the home assignment problem in home-based software distributed shared memory systems. An adaptive home migration protocol was proposed [54] to optimize the single-writer pattern which occurs frequently in distributed applications. This approach is unique in its use of a per-object threshold

which is continuously adjusted to facilitate home migration decisions. This adaptive threshold is monotonously decreasing with increased likelihood that a particular object exhibits a lasting single-writer pattern. The threshold is tuned according to the feedback of previous home migration decisions at runtime.

The adaptive home migration protocol was implemented in a distributed Java virtual machine that supports truly parallel execution of multithreaded Java applications on clusters. The analysis and the experiments show that home migration protocol demonstrates both the sensitivity to the lasting single-writer pattern and the robustness against the transient single-writer pattern.

A comparison between homeless and home-based Lazy Release Consistency (LRC) protocols which are used to implement Distributed Shared Memory (DSM) in cluster computing was done in Homeless and home-based Lazy Release Consistency protocols on Distributed Shared Memory [58]. A performance evaluation of parallel applications running on homeless and home-based LRC protocols was performed. Based on the performance comparison between Tread-Marks, which uses homeless LRC protocol, and home-based DSM system, it was shown that the home-based DSM system had better scalability than TreadMarks in parallel applications. This poor scalability in the homeless protocol is caused by a hot spot and garbage collection, but it was shown that these factors do not affect the scalability of the home-based protocol.

Some of the challenges present in providing support for OpenMP applications on a Software Distributed Shared Memory(DSM) based cluster system was carried in the work [28] Towards OpenMP Execution on Software Distributed Shared Memory Systems. The Treadmarks Software DSM system used as reference DSM for testing OPENMP programs wherein, shared memory sections can be allocated on-request. OpenMP workshare constructs are translated in the usual method, by modifying lower and upper bound of the loops according to the iteration space assigned for each participating process. Static scheduling was only supported. All parallel constructs are placed between a pair of barrier synchronizations. The barriers perform the dual functions of synchronization and maintaining coherence of shared data. The translation of serial program sections became non-trivial. The need to maintain correct

control flow precludes the possibility of executing the serial section by only the master process.

Detailed measurements of the performance characteristics of realistic OpenMP applications from the SPEC OMP2001 benchmarks were used for performance monitoring. The pitfalls of a naive translation approach from OpenMP into the API provided by a Software DSM system, and arrive at a set of possible program optimization techniques were proposed to overcome these.

## 2.1.2 Compiler Based SDSMs

A simple model of *shared data-objects*, which extends the abstract data type model to support distributed programming is **Orca** [33,35]. The model essentially provides shared address space semantics, rather than message passing semantics, without requiring physical shared memory to be present in the target system. Based on this, a new programming language Orca, based on shared data-objects is proposed and implemented. A compiler and three different run time systems for Orca are available.

The distribution of objects among the participating processors is left entirely to the implementation. This decision significantly contributes to the simplicity of the language. The design of Orca allows the compiler and run time system to deal efficiently with the distribution of objects. There are no global objects (objects have to be passed as parameter), so the run time system can keep track of which processes can access which objects. The semantics of an operation invocation do not depend on whether the object and the invoker are on the same or different processors. This location independence makes it possible to move objects dynamically. Shared data can only be accessed via a well-defined set of operations. This enables the system to dynamically *replicate* objects. An operation can access only a single object, allowing indivisible operations to be implemented without using a complicated locking or version management scheme.

Orca is also a language for implementing parallel applications loosely coupled distributed systems. Unlike most languages for distributed programming, it allows processes on different machines to share data. Such data is encapsulated in data objects, which are instances of user-defined abstract data types. The implementation

of Orca takes care of the physical distribution of objects among the local memories of the processors. In particular, an implementation may replicate and/or migrate objects in order to decrease access times for objects and increase parallelism.

Orca is intended for distributed applications programming rather than systems programming, and is therefore designed to be a simple, expressive and efficient language with clean semantics. Processes in Orca can communicate through shared data, even if the processors on which they run do not have physical shared memory. The main novelty of proposed approach is the way access to shared data is expressed. Unlike shared physical memory (or distributed shared memory), shared data in Orca are accessed through user-defined high-level operations. The implementation of Orca's model takes care of the physical distribution of shared data among processors.

Current parallel programming languages require advanced run-time support to implement communication and data consistency. As such, run-time systems are usually layered on top of a specific operating system, they are non portable.

Panda [36] is a portable virtual machine that provides general and flexible support for implementing run-time systems for parallel programming languages. Panda has two interfaces: a Panda interface, providing threads, RPC, and totally-ordered group communication, and a system interface which encapsulates machine dependencies by providing machine-independent thread and communication abstractions. The interfaces were integrated with Unix implementation, and provide a portable and scalable run-time system for the Orca parallel programming language on top of Panda.

**TreadMarks** [7]: A DSM system consisting of N networked workstations, each with its own memory. The DSM software provides the abstraction of a globally shared memory, in which each processor can access any data item without the programmer having to worry about where the data is or how to obtain its value.

TreadMarks provides shared memory as a linear array of bytes via a relaxed memory model called release consistency. The implementation uses the virtual memory hardware to detect accesses, but it uses a multiple-writer protocol to alleviate problems caused by mismatches between page size and application granularity. TreadMarks runs at the user level on Unix workstations without kernel modifications

or special privileges and with standard Unix interfaces, compilers, and linkers. TreadMarks implements inter machine communication using UDP/IP through the Berkeley sockets interface. Since UDP/IP does not guarantee reliable delivery, TreadMarks uses lightweight, operation-specific, user level protocols to ensure message arrival. Every message sent by TreadMarks is a request or a response.

Shasta[4,5] is compiler based software distributed shared memory(SDSM). Shasta supports a shared address space in software across a cluster of computers with physically distributed memory. A unique aspect of Shasta compared to most other software distributed shared memory systems is that shared data can be kept coherent at a fine granularity. Shasta achieves this by inserting inline code that checks the cache state of shared data before each load or store. In addition, Shasta allows the coherence granularity to be varied across different shared data structures in a single application. This approach alleviates potential inefficiencies that arise from the fixed large (page-size) granularity of communication typical in most software shared memory systems.

Shasta incorporates compilation checks of data before each load or store in an application. The address space is divided into lines and blocks matching with the cache lines and multiples of cache lines. The system is so organized that the block size and address generation differs for different address ranges. It also maintains a compilation checks for the loads and stores and as such this will lead to better performance. It employs exclusive shared and dirty modes of a block and the coherence is maintained with the help of these states. However, allowing processors to share memory within the same SMP is complicated by race conditions that arise because the inline state check is non-atomic with respect to the actual load or store of shared data. A novel protocol that avoids such race conditions without the use of costly synchronization in the inline checking code.

The protocol also includes optimizations such as non-blocking stores that aggressively exploit a relaxed memory consistency model. Other optimizations include detection of migratory data sharing, issuing multiple load misses simultaneously, merging of load and store misses to the same cache line, and support for prefetching and home placement directives.

Since Shasta supports shared memory entirely in software, it provides considerable flexibility in managing coherence granularity and applying protocol optimizations. The ability to support multiple coherence granularities within a single application is by far the most unique and important feature of Shasta, leading to performance improvements of as high as two times.

Compiler based prefetching for pointer-based applications in particular, those containing recursive data structures was studied [30] in Compiler-based prefetching for recursive data structures. Software-controlled data prefetching offers the potential for bridging the ever-increasing speed gap between the memory subsystem and today's high-performance processors. While prefetching has enjoyed considerable success in array-based numeric codes, its potential in pointer-based applications has remained largely unexplored. The fundamental problem in prefetching pointer-based data structures was analyzed and a guideline for devising successful prefetching schemes was proposed. Based on this guideline, designed three prefetching schemes, automated the most widely applicable scheme (*greedy prefetching*) in an optimizing research compiler, and evaluated the performance of all three schemes on a modern superscalar processor similar to the MIPS R10000.

These results demonstrate that compiler inserted prefetching can significantly improve the execution speed of pointer-based codes as much as 45% for the applications, compared with the only other compiler-based pointer prefetching scheme in the literature.

Cache-coherent multiprocessors with distributed shared memory are becoming increasingly popular for parallel computing. However, obtaining high performance on these machines requires that an application execute with good data locality. In addition to making effective use of caches, it is often necessary to distribute data structures across the local memories of the processing nodes; thereby reducing the latency of cache misses [25]. A set of abstractions for controlling loop scheduling and data distribution on CC-NUMA architectures and the implementation of these abstractions within a production compiler were taken up. The unique aspects include extensive error detection features, support for separate compilation across multiple files, optimization techniques to generate efficient code for distributed arrays, and tight integration of data distribution optimizations with other loop-level optimizations

in the compiler. Networks of workstations offer inexpensive and highly available high performance computing environments.