# Empirical Performance Studies on Implications of Shared Memory Hierarchy Resources in Multicore Computing Systems

A thesis submitted in fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

by Jitendra Kumar Rai

Department of Computer & Information Sciences

University of Hyderabad

Hyderabad - 500046

INDIA

October 2012

#### **CERTIFICATE**

This is to certify that the thesis work entitled "Empirical Performance Studies on Implications of Shared Memory Hierarchy Resources in Multicore Computing Systems" submitted by Jitendra Kumar Rai bearing Reg. No. 06MCPC04 in fulfillment of the requirements for the award of the degree of Doctor of Philosophy (Computer Science) of the University of Hyderabad, is a bona fide work carried out by him under our supervision.

The matter embodied in this thesis has not been submitted previously in part or in full to this or any other University or Institution for the award of any degree or diploma.

#### Dr. Atul Negi

(Supervisor)

Department of Computer & Information

Sciences (DCIS)

University of Hyderabad

Hyderabad-500056, INDIA

#### Dr. Rajeev Wankar

(Supervisor)

Department of Computer & Information

Sciences (DCIS)

University of Hyderabad

Hyderabad-500056, INDIA

#### HEAD

Department of Computer & Information Sciences (DCIS) University of Hyderabad Hyderabad-500056, INDIA

#### DEAN

School of Mathematics & Computer and Information Sciences University of Hyderabad Hyderabad-500056, INDIA

#### **DECLARATION**

I, Jitendra Kumar Rai, hereby declare that the work presented in this thesis entitled "Empirical Performance Studies on Implications of Shared Memory Hierarchy Resources in Multicore Computing Systems" has been carried out by me under the supervision of Dr. Atul Negi and Dr. Rajeev Wankar as per the Ph.D. ordinances of the University. I also declare that it has not been submitted previously in part or in full to this University or any other University or Institution for the award of any degree or diploma.

Jitendra Kumar Rai Reg. No. 06MCPC04

#### Acknowledgements

This thesis has been made possible by generous support of many people. My supervisors Dr. Atul Negi and Dr. Rajeev Wankar have provided the guidance and wisdom. I am also grateful to members of Doctoral Review Committee, especially Dr. Arun Agarwal and Dr. Hrushikesh Mohanty as well as the faculty members of the Department of Computer & Information Sciences, who reviewed the work and provided directions for further explorations. I also thank the Head of the Department of Computer & Information Sciences, for the encouragement.

I am also thankful to Director ANURAG, Hyderabad, for support and encouragement. I thank all the members of the Department of Computer & Information Sciences and ANURAG, who in some or other way provided support.

I also express my thanks to developers and users of open source software tools, especially Stephane Eranian and Corey Ashford of perfmon2; Peter Reutemann, Mark Hall and Harri M.T. Saarikoski of weka. I thank the anonymous reviewers, who reviewed part of the work sent for publication.

I would like to thank my family members especially my parents and wife for their understanding and support. I express my gratitude to the almighty, without whose blessings nothing is possible.

#### Abstract

Multicore processor architectures evolved and became dominant in recent years. It is mainly due to the diminishing returns from the efforts to increase the performance with single execution core on the chip. However multicore architectures involve sharing of resources especially the memory hierarchy resources such as processor caches, prefetchers and bus among the cores. This sharing may cause performance degradation of the programs co-running on multicore processors as compared to their solo run performance.

In the literature attempts to solve this problem proposed analytical models, which are very complex and difficult for use in real systems. Many of the previous works proposed specialized support from processor hardware, which may take time to become available in future generations of multicore processors.

It is observed that programs running simultaneously on different cores of a multicore processor, have complex interactions due to the use of shared memory hierarchy resources. In this work, we take up a unique approach for modeling the performance implications of such interactions by applying machine learning techniques. Machine learning techniques focus on methods that learn to recognize complex patterns from data. Here we give emphasis to empirical model building.

The work demonstrates the application of machine learning techniques to build models for characterization and performance prediction on multicore processor based systems. By characterization, we mean to characterize program memory behavior especially with respect to utilization of shared caches on multicore processors. The model developed for the program memory behavior characterization is later-on used for improving the process scheduling (i.e. CPU scheduling) on multicore processors. We also developed methodology to build a model that predicts performance on multicore processors. Such methodologies can further be utilized in performance oriented research on multicores. We describe the application of the built model for improving the multicore simulation in the AKULA tool-set. AKULA has been recently developed by researchers for rapid prototyping and evaluation of scheduling algorithms for multicore processors.

The efficacy of the developed methodologies to build the models, was validated using existing commodity multicore processor based systems. We observed that machine learning techniques are helpful in performance related studies on multicore processor based computing systems. We observed performance improvement up to 76% for 4-cores and 54% for 8-cores as compared to default linux kernel process scheduler on our experimental multicore platform by im-

proving process scheduling. The process scheduling was improved by utilizing the model developed using machine learning techniques, so that the interference among the co-running programs due to usage of resources shared among the cores is mitigated. The approximate average cost of the model was about 0.00075% of the total time (i.e. 7-8 cycles per million cycles), as observed in the experiments. Thus here we demonstrate that machine learning methods have been effective in building program performance models on existing commodity multicore based platforms.

# Contents

| Ti           | itle F | Page    |                                                     | j   |

|--------------|--------|---------|-----------------------------------------------------|-----|

| C            | ertifi | cate    |                                                     | i   |

| D            | eclar  | ation   |                                                     | iii |

| A            | ckno   | wledge  | ements                                              | iv  |

| $\mathbf{A}$ | bstra  | ıct     |                                                     | v   |

| Li           | st of  | Table   | S                                                   | х   |

| Li           | st of  | Figur   | es                                                  | xii |

| Li           | st of  | Publi   | cations                                             | xiv |

| 1            | Inti   | oduct   | ion                                                 | 1   |

|              | 1.1    | Motiv   | $\operatorname{ation}$                              | 2   |

|              |        | 1.1.1   | Evolution of Processor Architecture                 | 2   |

|              |        | 1.1.2   | Performance Related Studies                         | 8   |

|              |        | 1.1.3   | Commodity Multicore Processors                      | S   |

|              | 1.2    | Resea   | rch Objectives and Problem Statement                | 11  |

|              | 1.3    | Resea   | rch Contributions                                   | 12  |

|              | 1.4    | Organ   | nization of the Thesis                              | 14  |

| 2            | Rev    | view of | Performance Studies and Related Background          | 17  |

|              | 2.1    | Share   | d Memory Hierarchy Related Studies                  | 17  |

|              |        | 2.1.1   | Hardware Based Solutions                            | 18  |

|              |        | 2.1.2   | Software Based Solutions                            | 21  |

|              |        | 2.1.3   | Our Approach for Program Memory Behavior Character- |     |

|              |        |         | ization                                             | 26  |

|              | 2.2    | Overv   | riew of Machine Learning Techniques                 | 26  |

|   | 2.3  | Performance Prediction                                           | 29         |

|---|------|------------------------------------------------------------------|------------|

|   |      | 2.3.1 Previous Studies on Performance Prediction                 | 30         |

|   |      | 2.3.2 Our Approach for Performance Prediction                    | 31         |

|   | 2.4  | Conclusions                                                      | 32         |

| 3 | Cha  | racterization of Program Memory Behavior                         | 33         |

|   | 3.1  | Performance Issues on Multicores                                 | 34         |

|   | 3.2  | Program Memory Behavior                                          | 38         |

|   | 3.3  | Metric to Characterize Program Memory Behavior                   | 38         |

|   | 3.4  | Program Memory Behavior Characterization Issues                  | 42         |

|   | 3.5  | Hardware Performance Counters                                    | 43         |

|   | 3.6  | Machine Learning Algorithms Used                                 | 43         |

|   | 3.7  | Experimental Setup                                               | 44         |

|   |      | 3.7.1 Experimental Platforms                                     | 45         |

|   |      | 3.7.2 Processor Memory Hierarchy on Experimental Platforms       | 46         |

|   |      | 3.7.3 Workload                                                   | 47         |

|   | 3.8  | Methodology                                                      | 47         |

|   |      | 3.8.1 Solo-run Experiment                                        | 47         |

|   |      | 3.8.2 Concurrent-run Experiment                                  | 49         |

|   |      | 3.8.3 Generating Program Attributes and Class Variable           | 49         |

|   | 3.9  | Results on Prediction Accuracy for Predicting Solo-run Last      |            |

|   |      | Level Cache Stress                                               | 52         |

|   | 3.10 | Assessing Transferability of the Trained Models for Predicting   |            |

|   |      | Solo-run Last Level Cache Stress                                 | 55         |

|   |      | 3.10.1 Difference in Last Level Cache Organization on Intel Xeon |            |

|   |      | X5482 and Intel Core2 6300 Processors                            | 56         |

|   |      | 3.10.2 Prediction Accuracy Metrics of Trained Regression Mod-    |            |

|   |      | els on Test Data-set                                             | 56         |

|   | 3.11 | Conclusions                                                      | 57         |

| 4 | Imp  | roving Process Scheduling                                        | <b>5</b> 8 |

|   | 4.1  | Process Scheduler in Commodity OS                                | 58         |

|   | 4.2  | Process Scheduling Issues for Multicores                         | 60         |

|   | 4.3  | Role of Meta-scheduler                                           | 60         |

|   | 4.4  | Policy Framework of Meta-scheduler                               | 61         |

|   | 4.5  | Performance Evaluation of Meta-scheduler                         | 66         |

|   |      | 4.5.1 Experimental Platform                                      | 67         |

|   |      | 4.5.2 Workload                                                   | 67         |

|   |      | 4.5.3 Experiments                                                | 68         |

|    | 4.6   | Results                                                     |          | 69  |

|----|-------|-------------------------------------------------------------|----------|-----|

|    | 4.7   | Conclusions                                                 |          | 72  |

| 5  | Per   | Formance Prediction                                         |          | 73  |

|    | 5.1   | Experimental Setup                                          |          | 74  |

|    |       | $5.1.1  \text{Experimental Platforms}  \dots  \dots  \dots$ |          | 74  |

|    |       | 5.1.2 Processor Memory Hierarchy on the Experiment          | al Plat- |     |

|    |       | forms                                                       |          | 76  |

|    | 5.2   | Experiments                                                 |          | 77  |

|    | 5.3   | Generation of Solo-run Program Attributes & Class Var       | iable    | 78  |

|    | 5.4   | Results on Prediction Accuracy for Predicting Concurr       | ent-run  |     |

|    |       | Performance                                                 |          | 82  |

|    | 5.5   | Assessing Transferability of Model for Predicting Concurr   | ent-run  |     |

|    |       | Performance                                                 |          | 84  |

|    |       | 5.5.1 Differences in Last Level Cache Organization on       | Proces-  |     |

|    |       | sors used to Generate Train-set and Test-set Dat            | a        | 85  |

|    |       | 5.5.2 Prediction Accuracy Metrics of Trained Regression     | on Mod-  |     |

|    |       | els on Test Data-set                                        |          | 86  |

|    | 5.6   | Application of Machine Learning Based Performance Pro-      |          |     |

|    |       | for Multicore Simulation                                    |          |     |

|    |       | 5.6.1 Overview of the AKULA Tool-set                        |          |     |

|    |       | 5.6.2 Improving Multicore Simulation in AKULA               |          |     |

|    | 5.7   | Conclusions                                                 |          | 92  |

| 6  | Cor   | clusions and Future Work                                    |          | 94  |

|    | 6.1   | Summary of Contributions                                    |          | 94  |

|    | 6.2   | Conclusions                                                 |          | 96  |

|    | 6.3   | Future Work                                                 |          | 97  |

| Re | efere | nces                                                        |          | 101 |

| A  | Per   | mon2 Interface                                              |          | 115 |

| В  | WF    | KA Machine Learning Workbench                               |          | 117 |

# List of Tables

| 1.1 | List of some of the commodity multicore processors                  | 10 |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Solo-run and concurrent-run performance of SPEC cpu2006 pro-        |    |

|     | grams on Intel Xeon X5482 processor                                 | 34 |

| 3.2 | Percentage degradation in performance of some of the SPEC           |    |

|     | cpu2006 programs during concurrent-run as compared to their         |    |

|     | solo-run on Intel Xeon X5482 processor                              | 36 |

| 3.3 | Specifications of DELL Precision T7400 workstation used for         |    |

|     | generating data to build regression models                          | 45 |

| 3.4 | Specifications of DELL Precision 390 workstation used for gen-      |    |

|     | erating data to test regression models                              | 45 |

| 3.5 | Sample of train-set data of program memory behavior from Intel      |    |

|     | Xeon X5482 processor                                                | 51 |

| 3.6 | Prediction accuracy metrics achieved in 10 times 10-fold cross      |    |

|     | validation for predicting solo-run last level cache stress on Intel |    |

|     | XeonX5482 processor                                                 | 54 |

| 3.7 | Time taken for training the algorithms to build regression models   |    |

|     | for predicting solo-run last level cache stress                     | 55 |

| 3.8 | Last level cache related data of Intel Xeon X5482 and Intel Core2   |    |

|     | 6300 processors                                                     | 56 |

| 3.9 | Prediction accuracy of trained models on test data from Intel       |    |

|     | Core2 6300 for predicting solo-run last level cache stress          | 57 |

| 4.1 | Specifications of the experimental platform used for performance    |    |

|     | evaluation of intelligent scheduling done by meta-scheduler         | 67 |

| 4.2 | Description of SPEC cpu2006 applications used in performance        |    |

|     | evaluation with meta-scheduler                                      | 67 |

| 4.3 | Sets of SPEC cpu2006 applications used for performance evalu-       |    |

|     | ation with meta-scheduler                                           | 68 |

| 4.4 | Characteristics of the workload sets used for performance evalu-    |    |

|     | ation with meta-scheduler                                           | 68 |

|     |                                                                     |    |

| 4.5          | $IPC$ , $IPC_M$ and normalized speedup for various sets of work-                                                    |      |

|--------------|---------------------------------------------------------------------------------------------------------------------|------|

|              | loads in 4-core experiments on Intel quad-core Xeon X5482 pro-                                                      |      |

|              | cessor based platform                                                                                               | 70   |

| 4.6          | $IPC$ , $IPC_M$ and normalized speedup for various sets of work-                                                    |      |

|              | loads in 8-core experiments on Intel quad-core Xeon X5482 pro-                                                      |      |

|              | cessor based platform                                                                                               | 71   |

| 5.1          | Specifications of AMD quad-core Phenom 9650 processor based                                                         |      |

|              | platform used for generating data to test regression models built                                                   |      |

|              | for performance prediction                                                                                          | 75   |

| 5.2          | Specifications of AMD triple-core Phenom 8450 processor based                                                       |      |

|              | platform used for generating data to test regression models built                                                   |      |

|              | for performance prediction                                                                                          | 75   |

| 5.3          | Sample of train-set data for performance prediction collected                                                       |      |

|              | from Intel Xeon X5482 processor                                                                                     | 83   |

| 5.4          | Prediction accuracy results from 10 times 10-fold cross validation                                                  |      |

|              | for predicting concurrent-run performance on Intel Xeon X5482                                                       |      |

|              | processor                                                                                                           | 84   |

| 5.5          | Time taken to build regression models using train-set having                                                        |      |

|              | 3025 instances from Intel Xeon X5482 processor for predicting                                                       |      |

|              | concurrent-run performance                                                                                          | 84   |

| 5.6          | Last level cache related data of Intel Xeon X5482, Intel Core2                                                      |      |

|              | 6300, AMD Phenom 9650 and AMD Phenom 8450 processors                                                                | ~ ~  |

|              | used in performance prediction experiments                                                                          | 85   |

| 5.7          | Prediction accuracy of the trained model on test data from Intel                                                    | 0.0  |

| <b>F</b> 0   | Core2 6300 processor for predicting concurrent-run performance.                                                     | 86   |

| 5.8          | Prediction accuracy of the trained model on test data from AMD                                                      | 0.0  |

| <b>F</b> 0   | Phenom 9650 processor for predicting concurrent-run performance.                                                    | 80   |

| 5.9          | Prediction accuracy of the trained model on test data from AMD                                                      | 0.0  |

| F 10         | Phenom 8450 processor for predicting concurrent-run performance.                                                    | 86   |

| 0.10         | Example solo-run performance data used by AKULA bootstrap                                                           | 90   |

| <u></u> 5 11 | module for multicore simulation                                                                                     | 89   |

| 0.11         | Example performance degradation matrix for concurrent-run, used by AKULA bootstrap module for multicore simulation. | 89   |

|              | THOSE DV LEES VILLE VOORMAN HOURIE IOL HUUROOF SUUULAMOH                                                            | ().7 |

# List of Figures

| 1.1 | Schematic views of singlecore processors                                                                                                                         | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Schematic views of multicore and multicore-multithreaded pro-                                                                                                    |    |

|     | cessors                                                                                                                                                          | 7  |

| 1.3 | Thesis organization                                                                                                                                              | 15 |

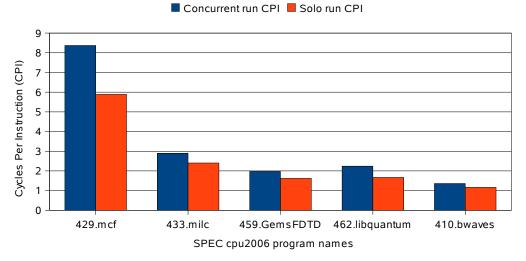

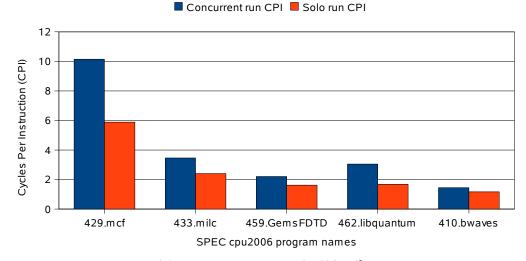

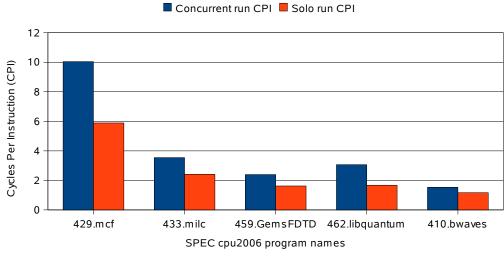

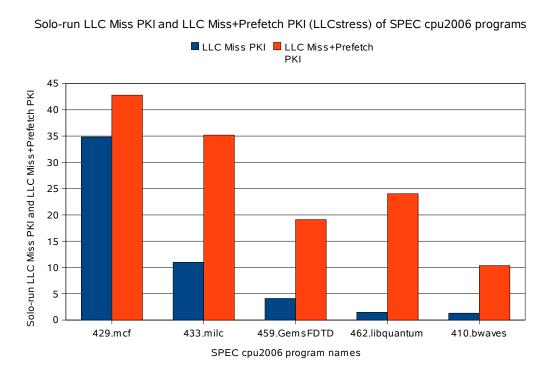

| 3.1 | Concurrent-run and solo-run performance of some of the SPEC cpu2006 benchmarks on Intel quad-core Xeon X5482 processor                                           | 36 |

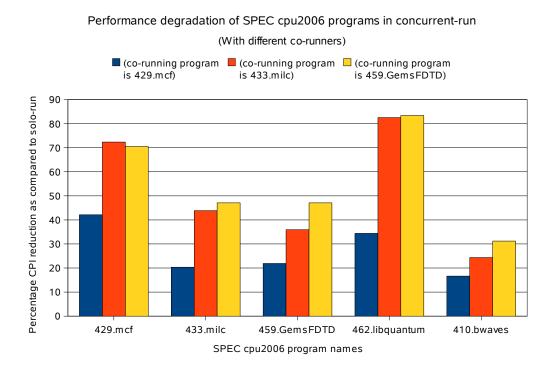

| 3.2 | Percentage degradation in performance of some of the SPEC cpu2006 programs during concurrent-run as compared to their                                            |    |

| 3.3 | solo-run on Intel Xeon X5482 processor.  Concurrent-run and solo-run last level cache (LLC) stress of SPEC cpu2006 benchmark program 429.mcf on Intel Xeon X5482 | 37 |

|     | processor                                                                                                                                                        | 39 |

| 3.4 | Suitability of solo-run last level cache stress as a metric to char-                                                                                             |    |

| 3.5 | acterize the program memory behavior                                                                                                                             | 40 |

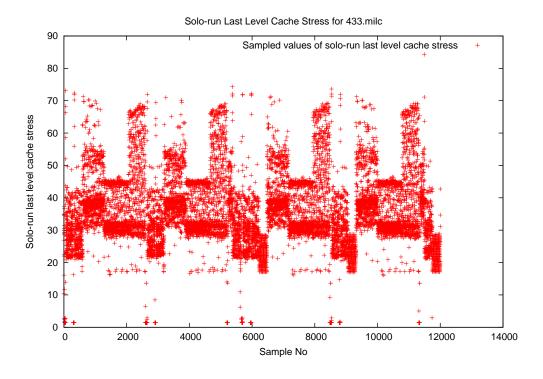

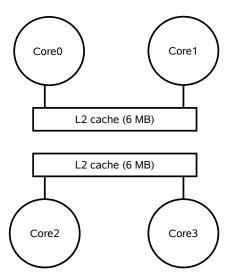

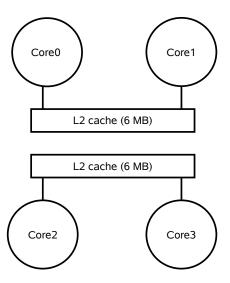

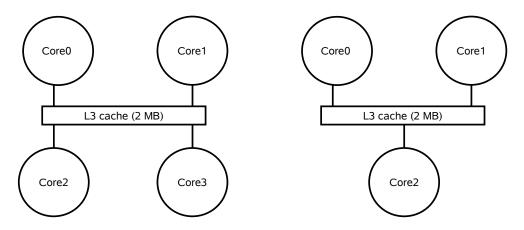

| 3.6 | on Intel Xeon X5482 processor.  Last level (L2) cache sharing on Intel Xeon X5482 processor used                                                                 | 41 |

|     | for generating data to build regression models                                                                                                                   | 46 |

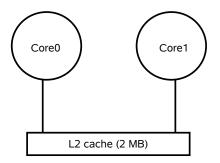

| 3.7 | Last level (L2) cache sharing on Intel Core2 6300 processor used                                                                                                 |    |

| 3.8 | for generating data to test regression models                                                                                                                    | 47 |

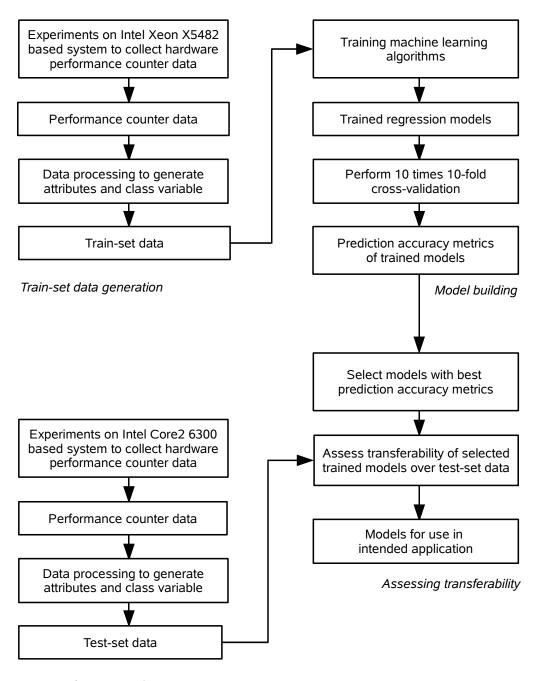

| 3.0 | learning algorithms                                                                                                                                              | 48 |

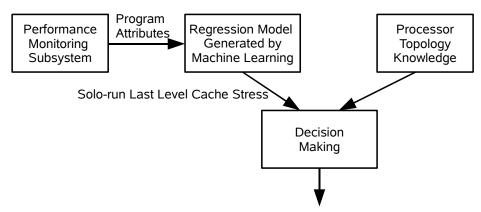

| 4.1 | Block diagram of the meta-scheduler                                                                                                                              | 62 |

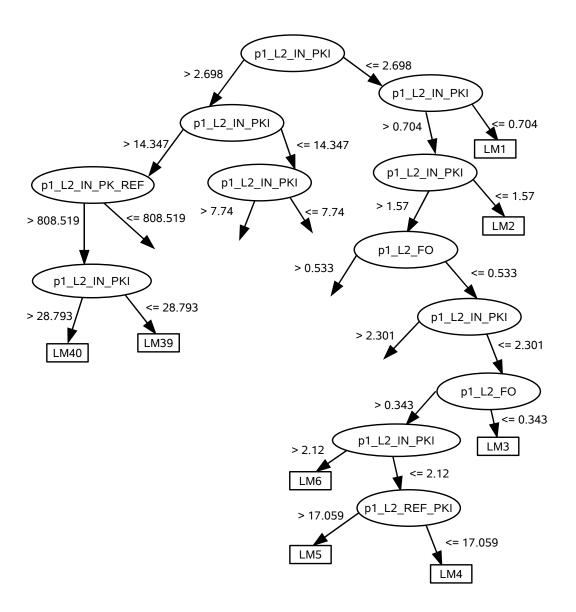

| 4.2 | Part of built model tree used by meta-scheduler                                                                                                                  | 64 |

| 4.3 | Topology of Intel quad-core Xeon X5482 processor                                                                                                                 | 66 |

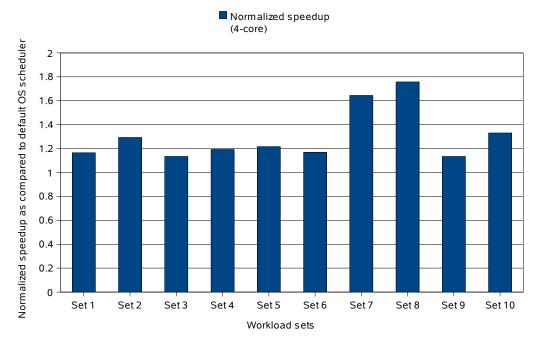

| 4.4 | Normalized speedup with meta-scheduler in 4-core experiments                                                                                                     |    |

|     | on Intel quad-core Xeon X5482 processor based platform                                                                                                           | 70 |

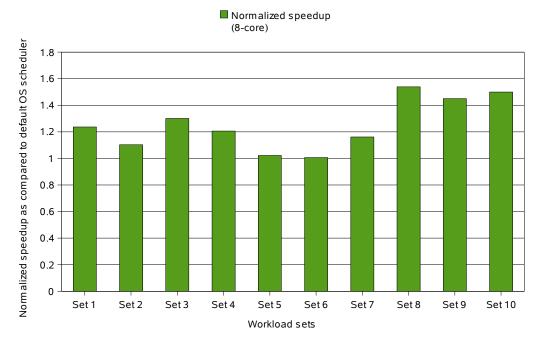

| 4.5 | Normalized speedup with meta-scheduler in 8-core experiments                                                                                                     |    |

|     | on Intel quad-core Xeon X5482 processor based platform                                                                                                           | 71 |

| 5.1 | Last level (L3) cache sharing on AMD Phenom 9650 and AMD        |    |

|-----|-----------------------------------------------------------------|----|

|     | Phenom 8450 processors used for generating data to test regres- |    |

|     | sion models built for performance prediction                    | 76 |

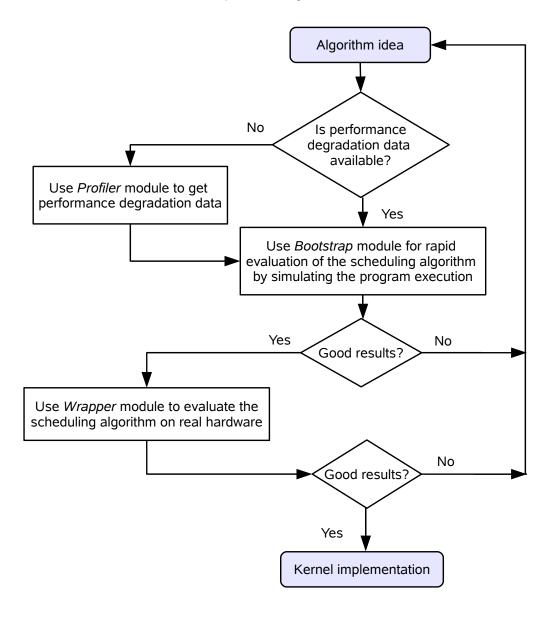

| 5.2 | Framework provided by AKULA tool-set                            | 88 |

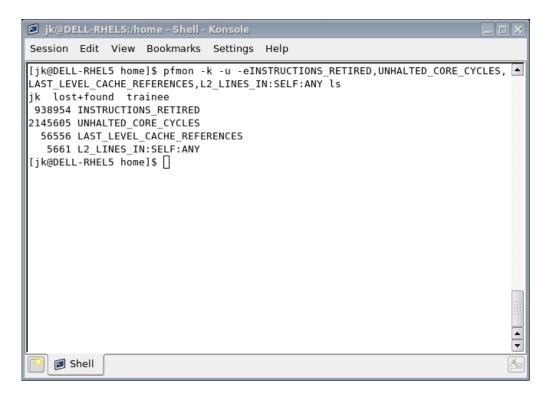

| A.1 | Output of Pfmon session on Intel quad-core Xeon X5482 proces-   |    |

|     | sor based experimental platform                                 | 16 |

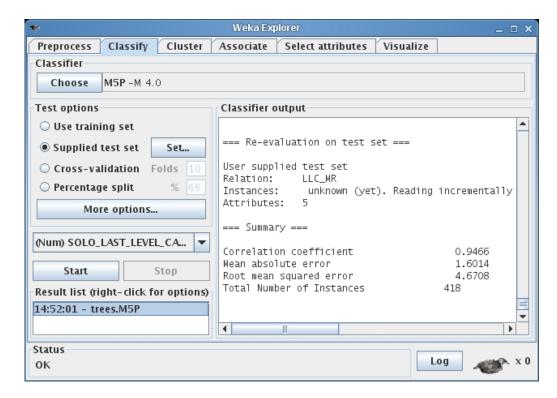

| B.1 | Output of Weka Explorer                                         | 18 |

#### List of Publications

#### Journals:

- J. K. Rai, A. Negi, R. Wankar and K. D. Nayak, "Characterizing L2 Cache behavior of Programs on Multi-core Processors: Regression Models and Their Transferability", International Journal of Computer Information Systems and Industrial Management Applications (IJCISIM), ISSN: 2150-7988 vol. 2 (2010), pp. 212–221. http://www.mirlabs.org/ijcisim.

- J. K. Rai, A. Negi, R. Wankar and K. D. Nayak, "A Machine Learning based Meta-Scheduler for Multi-core Processors", *International Journal of Adaptive, Resilient and Autonomic Systems (IJARAS)*, ISSN: 1947-9220 vol. 1, no. 4, (2010), IGI-Global, USA, 2010, pp. 46–59.

- Also appeared in *Machine Learning: Concepts, Methodologies, Tools and Applications*, ed. Information Resources Management Association, USA, 2012, pp. 522–534, doi:10.4018/978-1-60960-818-7.ch311.

- J. K. Rai, A. Negi and R. Wankar, "Using Machine Learning Techniques for Performance Prediction on Multi-cores", *International Journal of Grid and High Performance Computing (IJGHPC)*, ISSN: 1938-0259 vol. 3, no. 4, (2011), IGI-Global, USA, 2011, pp. 14–28.

Also in Applications and Developments in Grid, Cloud, and High Performance Computing, ed. Emmanuel Udoh, IGI-Global, USA, 2013, pp. 259-273, doi: 10.4018/978-1-4666-2065-0.ch017.

#### **Conferences:**

- J. K. Rai, A. Negi, R. Wankar and K.D. Nayak, "Using Machine Learning to Characterize L2 Cache behavior of Programs on Multicore Processors", in *Proceedings of 2009 International Conference on Artificial Intelligence and Pattern Recognition (AIPR-09)*, Orlando, Florida, USA July 13-16, 2009, pp. 301–306.

- J. K. Rai, A. Negi, R. Wankar and K. D. Nayak, "On Prediction Accuracy of Machine Learning Algorithms for Characterizing Shared L2 Cache behavior of Programs on Multicore Processors", in *Proceedings of The 2009*

- IEEE International Conference on Computational Intelligence, Communication Systems and Networks (CICSyN2009), Indore, India, July 23-25, 2009, pp. 213–219.

- J. K. Rai, A. Negi, R. Wankar and K. D. Nayak, "Characterizing L2 Cache behavior of Programs on Multi-core Processors: Regression Models and their Transferability", in *Proceedings of The Eighth IEEE International conference on Computer Information Systems and Industrial Management Applications (CISIM 2009)*, held in conjunction with World Congress on Nature Biologically Inspired Computing 2009, (NaBIC 2009), Coimbatore, India, Dec. 09-11, 2009, pp. 1673–1676.

- J. K. Rai, A. Negi, R. Wankar and K. D. Nayak, "Performance Prediction on Multi-core Processors", in *Proceedings of The IEEE 2010 International Conference on Computational Intelligence, Communication Systems and Networks, (CICN 2010)*, Bhopal, India, Nov. 26-28, 2010, pp. 633–637.

- J. K. Rai, A. Negi and R. Wankar, "Machine Learning Based Performance Prediction for Multi-core Simulation", in *Proceedings of The 5<sup>th</sup> Multi-Disciplinary International Workshop on Artificial Intelligence MI-WAI 2011*, Hyderabad, India, Dec. 07-09, 2011, LNAI 7080, Springer-Verlag Berlin Heidelberg, pp. 236–247.

## Chapter 1

#### Introduction

This thesis is concerned with the interactions of software and emerging processor architecture, particularly multicore architecture. The cores present on multicore processors share various memory hierarchy resources such as processor caches, prefetchers and bus. The sharing of memory hierarchy resources among programs simultaneously running on different cores of a multicore processor, causes those programs to have complex interactions. These interactions may result in severe performance degradations. The thesis work involves modeling the performance implications of such interactions.

Previous research works (details of the previous works are given in chapter 2) proposed analytical models for program behavior with respect to use of memory hierarchy resources (especially caches). These models are fairly complex to be used in real systems. Some of the previous works proposed specialized support from processor hardware for this purpose. It may take time for such specialized support to become available on commodity multicore processors.

The thesis work uses machine learning techniques for modeling the performance implications of shared memory hierarchy resources in multicore computing systems. The discipline of machine learning provides techniques, which can be applied to automatically learn the complex patterns and make intelligent decisions based on data.

We measure how a selection of workloads perform on multicore processors and investigate how data driven methods such as machine learning techniques can be effectively utilized to build models for some of the performance critical aspects of computing systems based on these processors. As part of the study, we also explore the utilization of the built models for improving the process (i.e. CPU) schedule on multicores and simulation of multicore processors.

The chapter is organized as follows: Section 1.1 provides the motivation behind the work carried-out in the thesis. In section 1.2, we state the research

objectives and the problem statement. In section 1.3, we mention the research contributions of the thesis. Section 1.4 provides organization of the thesis.

#### 1.1 Motivation

The motivation for the work basically comes from the developments in processor architecture and associated performance studies. Some of which, especially by Herescu et al. [1] and Fedorova et al. [2] identified the performance issues with emerging multicore architectures. We begin with an overview of the evolution of processor architecture in section 1.1.1. The architectural developments induce new research avenues, involving performance evaluations and characterization of the new upcoming systems. Section 1.1.2 provides a brief description of performance and characterization studies, which have been associated with the evolution of the processor architecture. Section 1.1.3 provides information on some of the commodity multicore processors available in the market that reflects the trend towards growth in number of cores.

#### 1.1.1 Evolution of Processor Architecture

In this section, a review of developments in the processor architecture is given. We begin with the single-core processor architecture and describe the evolution towards multicores. We also mention the reasons, why the multicore architecture became prevalent and why they seem to be the computing engines for future platforms.

The first microprocessor that became commercially available was Intel 4004 [3]. It was released in year 1971. Over the past four decades, the microprocessor industry has seen consistent gains in application performance as a result of multiplicative effect of growth in transistor count and higher clock frequencies. The growth in transistor count has been the result of Moore's law. Gordon Moore predicted in the year 1975, that the number of transistors on an integrated circuit would double every two years [4]. This actually was a revision of his earlier prediction made in the year 1965, according to that the number of transistors would double every year [5]. The advances in the integrated circuit manufacturing technology made it possible to shrink the circuit elements, which allowed more and more transistors to be placed in a single microprocessor.

The three main areas, which contributed to performance gains in the past are clock speed, execution optimization and cache [6]. Increasing the processor clock speed resulted in getting more cycles, which increased the speed at which the central processing unit (CPU) performed the work. Optimizing execution flow is about doing more work per cycle. It includes having more powerful instructions as well as various other optimizations like pipelining, branch prediction, making the pipelines deep and superscalar architectures [7]. Pipelining involves executing different sub-steps of sequential instructions simultaneously. Branch prediction allows processors to fetch and execute instructions without waiting for a branch to be resolved. Increasing the depth of pipeline (also called superpipelining) means using a longer pipeline with more stages. It was introduced to have architecture with more stages, where each stage does less work so that the processor can be scaled to higher clock frequency. Superscalar architectures include parallel execution units, which can execute instructions simultaneously. Processors were provided with bigger and multiple level of caches so that frequently accessed instructions and data can be kept in the fast accessed caches. This reduced the latency caused due to frequent memory access.

Out of order processing involves executing instructions in an order different from the order they appear in the program. It emerged as an execution optimization technique for execution efficiency to utilize the CPU while it stalled on memory. Out of order execution strove for instruction-level parallelism (ILP) within a sequence of instructions, or thread of control. It required knowing what instruction the program will execute in the future. Programs have branches and CPU needs to predict which instructions will be executed after the branch and predicting the future is difficult. The reliance on a single thread of control to find instruction-level parallelism limits the parallelism available for many applications, and the cost of extracting parallelism from a single thread became prohibitive due to large increase in overall complexity.

The performance scaling in the single core processors largely through increasing clock speed almost touched its limit. As the chip geometries shrink and clock speeds rise, the transistor leakage current increases, which leads to excessive power consumption and heat. The advantages of increased clock speed are also negated by memory latency, as the memory access speeds are not scaling on par with processor clock speeds. There is large and growing mismatch between the processor (CPU) and off-chip main memory in terms of speed as well as bandwidth. Many researchers have referred to this problem as "memory / bandwidth wall" in their works [8] [9] [10].

Another paradigm emerged to improve utilization of CPU resources by leveraging on thread and process level parallelism. A single physical processor can have one or multiple cores and each core can have one or multiple hardware threads. A single core processor with multiple hardware threads is called multithreaded processor while a multicore processor having multiple hardware threads per core is also called multicore-multithreaded or chip-multithreaded processor. The multicore or chip-multiprocessing architectures provide a way to scale the performance, while keeping the heat dissipation and power consumption under limit [11]. Some of the approaches that emerged on the architecture front to exploit the parallelism are described as follows:

- 1. Multithreading (MT): The processor allows more than one thread of execution to exist on the CPU at the same time. It maintains hardware state (program counters and registers) for several threads. Some of the methods used to achieve multi-threading are mentioned as follows:

- Fine-grained Multithreading In one cycle the processor executes instructions from one of the threads. On the next cycle it switches to context of different thread and executes instructions from the new thread [12].

- Coarse-grained Multithreading Here a single context (thread) utilizes all the processor resources until it reaches a long-latency operation such as accessing memory due to cache miss, at that point the processor switches to another context (thread) [13].

- Interleaving A variant of fine-grained multithreading, where issuing of instructions is switched every cycle in round-robin manner between available contexts. Whenever a context encounters a long-latency operation, it becomes unavailable, in such case the processor squashes only those instructions in the pipeline which belong to the unavailable context [14][15].

- Simultaneous Multithreading It combines hardware features of wide-issue superscalars and multithreaded processors. It has the ability to issue multiple instructions each cycle like superscalars and it maintains hardware state for several programs (threads). Hence this processor can issue multiple instructions from multiple threads each cycle. It exploits both instruction-level and thread-level parallelism [16].

- 2. Chip-multiprocessing (CMP): It uses relatively simple single-thread processor cores on a die [17].

- 3. Chip-multithreading (CMT): Here each core on a die supports multiple hardware threads (contexts) [15].

# 4. Single ISA Heterogeneous (asymmetric) Chip Multiprocessors: It is a multicore processor where all the cores execute the same instruction set architecture (ISA) but have different performance and power characteristics. For example, on a single processor chip some cores are provided with wide issue and out of order processing capability while others are simple single issue CPUs [18].

5. Multiple ISA Heterogeneous (asymmetric) Chip Multiprocessors: These processors have cores that execute instructions belonging to different instruction set architectures (ISAs). They typically address data-level and instruction-level parallelism simultaneously. Any given instruction can not be executed on all the cores [19]

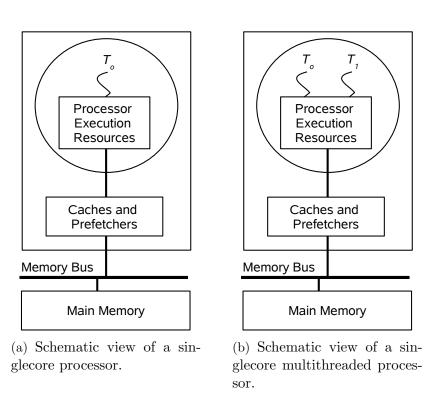

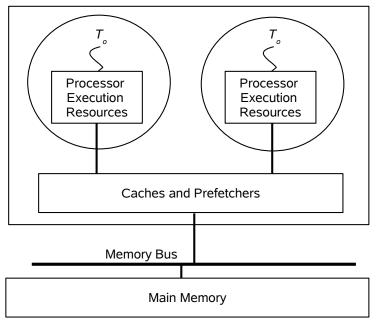

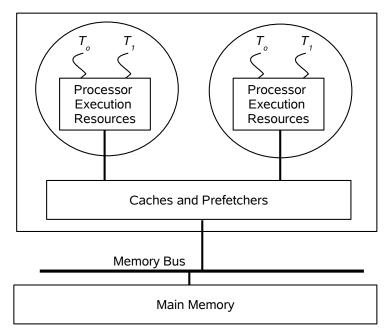

We show schematic views of variants of singlecore as well as multicore architectures in figure 1.1 and figure 1.2. For simplicity we have shown only one level of on-chip caches in all these schematic views. The on-chip cache shown here is last level cache and is unified in nature i.e. it contains both instructions and data.

Figure 1.1: Schematic views of singlecore processors. Here  $T_0$  and  $T_1$  are the hardware threads supported by the single core, which is shown as circle.

In figure 1.1a, we show schematic view of a singlecore processor. In this

processor there is one core present on the chip, which has the processor execution resources. There is single hardware thread  $T_0$  supported by the single core present on the chip. So there is single processor state maintained for the single hardware thread present on the core. Figure 1.1b shows schematic view of a singlecore multithreaded (MT) processor. In this a single core is present on the chip. The core supports two hardware threads  $T_0$  and  $T_1$ . There are two processor states maintained by the core, one state for each hardware thread. The two hardware threads present on the core share the execution resources by any of the previously mentioned methods used to achieve multi-threading. In this case apart from sharing some of the execution resources, the hardware threads  $T_0$  and  $T_1$  also share the resources present on the memory hierarchy of the processor. The memory hierarchy resources include the on-chip caches, prefetchers and interconnects such as memory bus.

Figure 1.2a shows schematic view of a multi-core processor. The processor chip contains two cores. Each core shown in figure, supports single hardware thread  $T_0$ . In this case hardware thread supported by each of the core has its own private execution resources. Both cores present on the chip share the resources present on the memory hierarchy of the processor i.e. on-chip caches, prefetchers and memory bus. In turn the hardware threads (each supported by one core) also share the same memory hierarchy resources of the processor.

Figure 1.2b shows schematic view of a multicore-multithreaded processor. The processor chip contains two cores. Each core shown in figure, supports two hardware threads  $T_0$  and  $T_1$ . There are two processor states maintained by each of the core, one state for each hardware thread. The two hardware threads present on each of the core share the execution resources of the core by any of the previously mentioned methods used to achieve multi-threading. Both cores present on the chip share the resources present on the memory hierarchy of the processor. In turn all the four hardware threads (two hardware threads supported by each core) also share the same memory hierarchy resources of the processor.

In a nutshell it can be said that following are the significant factors, which led towards development and commercial availability of multicore processors:

- Shift towards thread-level parallelism (TLP) instead of relying only on instruction-level parallelism (ILP) to achieve improvement in processor performance.

- Continual growth in the number of transistors available on the microprocessor chip due to Moore's law[4], so that available transistors could be

(a) Schematic view of multicore processor or chip-multiprocessor (CMP).

(b) Schematic view of multicore-multithreaded or chip-multithreaded (CMT) processor.

Figure 1.2: Schematic views of multicore and multicore-multithreaded processors. Here  $T_0$  and  $T_1$  are the hardware threads supported by the cores, which are shown as circles.

used to provide additional execution cores on the same chip.

- The uncoupling of processor speed from transistor count, due to shift to thread-level parallelism (TLP).

- Rising memory wall i.e. large and growing disparity between processor (CPU) speed and off-chip main memory speeds, in terms of both latency and bandwidth [8] [9] [10].

In fact researchers predicted about multicore being the dominant architecture of future microprocessors due to their better performance per watt characteristics [20], which is also reflected in industry trends [21].

#### 1.1.2 Performance Related Studies

In this section we provide a glimpse of performance related studies associated with architectural evolution, especially with the introduction of multiple hardware threads and cores on a single processor chip (details of the previous related works are given in chapter 2). Such studies include identifying the performance issues with emerging architectures and proposing the possible solutions to various problems encountered. Characterization of systems as well as workloads are one of the essential part of the performance studies [22]. The studies performed for the characterization of systems help in identifying the potential performance bottlenecks. In this way the characterization provides directions for further tuning the systems for better performance. The efforts towards performance improvement involve explorations of design space at the level of microarchitecture as well as software stack [23] [24]. The performance studies also help in creation of the workloads for future.

In year 1996, Olukotun et al. [25] advocated the multicore architecture for a general purpose processor. There have been several research projects to explore multi-core architecture like Hydra [26], Piranha [27] and Atlas [28]. These projects explored various issues such as microarchitectural design, compiler support, and speculative execution of user-level applications. In the past, performance studies have been done on simulators to analyze the operating system behavior in the presence of multiple hardware threads on a single processor [29]. Intel introduced hyperthreading (HT) on Xeon processor [30], which is an implementation of simultaneous multi-threading (SMT). On hyperthreaded Xeon processor, a single core supported two hardware threads. Hyperthreading makes a single physical processor appear as two logical processors; the physical execution resources are shared and the architecture state is duplicated for the

two logical processors. Initial performance analysis have been done by Tuck and Tullsen [31] over hyperthreaded Intel Pentium 4 processor [32]. The focus of the study was to understand its performance and the underlying reasons behind that performance. Bulpin and Pratt [33] measured the multiprogramming performance of Intel Pentium 4 processor with hyperthreading and confirmed the findings of previous study done by Tuck and Tullsen [31]. They observed the mutual effect of processes simultaneously executing on the Intel Pentium 4 processor, and found that many performance results can be explained by considering cache miss rates and resource requirement heterogeneity of those processes. The general rule of thumb derived from the study was that threads with high cache miss rates can have a detrimental effect on simultaneously executing threads. In a later work Bulpin and Pratt [34] proposed process scheduling heuristics for hyper-threaded processor, so that pathological combinations of workloads that can give a poor system-throughput could be avoided.

Among studies on multicore processors, Herescu et al. [1] performed performance workload characterization on platform based on IBM POWER5 [35] processor. IBM POWER5 is a dual core processor with simultaneous multithreading support. Each core on the processor supports two hardware threads. They observed performance impacts due to shared resources, such as caches, translation look-aside buffers (TLBs) and branch prediction hardware. Fedorova et al. [2] also made observation that the sharing of memory hierarchy on the processor such as last level caches among the cores may cause the corunning programs to suffer with performance degradations. In the next section we mention some of the commodity multicore processors, which reflect the trend towards growth in number of cores present on a single chip as well as sharing of processor caches among the cores / threads.

#### 1.1.3 Commodity Multicore Processors

In year 2001, IBM introduced the first chip containing two single-threaded processor cores – the POWER4 [36], for use in general purpose computing. Since that time, several other chip makers have also introduced their multicore solutions for general purpose computing.

We mention some of the commodity multicore processors in table 1.1. The number of cores on the chip are increasing along with generations of the processors. We also see that in majority of the emerging multicore processors the memory hierarchy resources (especially the last level caches L2 or L3) are shared among the cores.

Table 1.1: List of some of the commodity multicore processors.

| Year | Multicore Processor          | No    | On-      | Shared | Citations |

|------|------------------------------|-------|----------|--------|-----------|

|      |                              | of    | chip     | caches |           |

|      |                              | cores | caches   |        |           |

| 2001 | IBM POWER4                   | 2     | L1,L2    | L2     | [36]      |

| 2004 | IBM POWER5                   | 2     | L1,L2    | L2     | [35]      |

| 2005 | Intel Pentium                | 2     | L1,L2    | none   | [37]      |

| 2005 | AMD Opteron                  | 2     | L1,L2    | none   | [38]      |

| 2005 | IBM-Microsoft PowerPC Xenon  | 3     | L1,L2    | L2     | [39]      |

| 2005 | Sun UltraSPARC T1 (Niagara1) | 8     | L1,L2    | L2     | [40]      |

| 2006 | Intel Itanium 2              | 2     | L1,L2,L3 | none   | [41]      |

| 2006 | Sony-Toshiba-IBM Cell        | 9     | L1,L2    | none   | [42] [43] |

| 2006 | Intel Xeon & Core 2 Extreme  | 4     | L1,L2    | L2     | [44]      |

| 2007 | Sun-Fujitsu SPARC64 VI       | 2     | L1,L2    | L2     | [45]      |

| 2007 | IBM POWER6                   | 2     | L1,L2    | none   | [46]      |

| 2007 | AMD Opteron                  | 4     | L1,L2,L3 | L3     | [47]      |

| 2007 | Sun UltraSPARC T2 (Niagara2) | 8     | L1,L2    | L2     | [48]      |

| 2008 | Intel Xeon                   | 6     | L1,L2,L3 | L3     | [49]      |

| 2008 | Sun-Fujitsu SPARC64 VII      | 4     | L1,L2    | L2     | [50]      |

| 2009 | AMD Opteron                  | 6     | L1,L2,L3 | L3     | [51]      |

| 2010 | IBM POWER7                   | 8     | L1,L2,L3 | L3     | [52]      |

| 2010 | Intel Xeon                   | 8     | L1,L2,L3 | L3     | [53]      |

Multicore processors have introduced sharing of resources among multiple execution cores present on the processor chip. Resources shared among the execution cores include on-chip caches, hardware prefetchers and system bus. In contrast, in the previous generation single-core processors the aforementioned resources were private for the execution core. Previous performance studies, mainly by Bulpin and Pratt [33], Herescu et al. [1] and Fedorova et al. [2] identified processor memory hierarchy resources shared among the cores / threads of the processors as one of the performance critical resource. Sharing of the resources among the cores of the multicore processors causes co-running programs to interfere with each-other. The mutual interference among the corunning programs may cause them to suffer with performance degradations. Thus the multicore architecture poses additional performance issues that need to be addressed for effective utilization of the systems.

At present the multicore processors have become the driving engine for variety of computing systems such as desktops, servers, game consoles as well as embedded systems. The eminent ubiquity of the multicore processors indicates that multicore is going to be the dominant architecture of future. It makes imperative for us to look into performance issues arising due to interactions of multicore based systems and software. In next section we mention the research objectives and the problem statement for the thesis.

#### 1.2 Research Objectives and Problem Statement

We aim to come up with the models, which can address the performance issues caused due to sharing of memory hierarchy resources among the cores of the multicore processors. The processor memory hierarchy resources include caches, prefetchers and memory bus.

The major objectives of the thesis are to:

- Investigate the performance issues due to sharing of the processor memory hierarchy resources (such as processor caches, prefetchers and bus) among the cores of the multicore processors.

- Review the existing models for memory behavior of programs and associated performance aspects of the multicore processors.

- Propose models for program memory behavior and associated performance aspects of the multicore processors.

- Suggest prospective applications of the proposed models towards solving the performance issues of multicore processors.

The thesis addresses the performance issues of multicore processor based computing systems with focus on program behavior with respect to utilization of the memory hierarchy resources, which are shared among the cores of the processor. The following are the key concerns addressed in the thesis:

- How to develop a model to characterize the program memory behavior on multicore processors (described in section 3.8 of chapter 3 on page 47).

- How to devise a mechanism for application of model developed in previous step so that the interference among co-running programs due to usage of memory hierarchy resources shared among the cores is mitigated (described in section 4.4 of chapter 4 on page 61).

- How to develop a model for predicting the performance degradations caused due to sharing of the processor memory hierarchy resources among the co-running programs (described in section 5.2 and section 5.3 of chapter 5 on page 77 and 78 respectively).

• A prospective application of the model developed for predicting the performance degradations (described in section 5.6 of chapter 5 on page 87).

Overall the work aims at modeling the performance aspects of multicore processor based computing systems and prospective applications of the developed models. It considers use of machine learning techniques for building the models.

#### 1.3 Research Contributions

The domain of machine learning provides various techniques which can be used to build systems for characterizing complex phenomena. Programs simultaneously running on different cores of a multicore processor, have complex interactions due to usage of shared memory hierarchy resources. The thesis presents a unique approach for modeling the performance implications of such interactions by applying machine learning techniques.

The contributions that stem from our research are demonstrated by the publications generated from the thesis. The main contributions from the thesis could be summarized as follows:

- Methodology to build model to characterize program memory behavior on multicore processors: We proposed the methodology to build model to characterize program memory behavior on multicore processors. The methodology includes proposal of program attributes, using which the program memory behavior can be predicted in terms of solo-run last level cache stress. It involves use of machine learning techniques to capture the knowledge about processor memory hierarchy resource utilization behavior of running programs. The off-line trained model could be used later for guiding the system policies to mitigate the interference among the co-running programs due to usage of memory hierarchy resources shared among the cores.

- Meta-scheduler for multicore processors: We implemented a proof of concept meta-scheduler as an example application of the model developed for program memory behavior characterization. The meta-scheduler runs in user space and guides the process (CPU) scheduling decisions made by underlying operating system process scheduler so that the interference among the programs co-running on multicores is mitigated. We observed performance improvement up to 76% for 4-cores and 54% for 8-cores as compared to default linux kernel process scheduler on our

Intel quad-core Xeon X5482 processor based platform by improving process scheduling. The approximate average cost of the model was about 0.00075% of the total time (i.e. 7-8 cycles per million cycles), as observed in the experiments. The meta-scheduler does not require modifications in process scheduler of the operating system running on the platform.

- Methodology to build model for performance prediction on multicore processors: We also proposed the methodology to build model to predict the performance on multicore processors. The model takes the proposed solo-run program attributes as inputs and predicts the concurrent-run performance of the programs on multicores. The concurrent-run involves interference among the program and other programs co-running on cores, which share the memory hierarchy resources with the first program. Such models and techniques could be used for further performance oriented research on multicores as well as simulation of multicores.

- Application of performance prediction model for simulation of multicore processors: We also propose the prospective application of the model, which was developed for performance prediction in previous step. We describe the use of the model for simulation of multicores in AKULA tool-set [54], which was recently developed by Zhuravlev et al. for rapid prototyping and evaluation of scheduling algorithms for multicore processors. The use of machine learning based model adds the performance predictability to enable the multicore simulation for workload combinations for which the concurrent-run performance data is not available. The approach proposed in the thesis also supports simulation for processors having variable number of processor cores sharing the resources. For example, the number of cores sharing last level caches are four on Intel Xeon E5630 [55], three on AMD Phenom 8450 [56] and four on AMD Phenom 9650 [56] processors.

The models and the prototype meta-scheduler were developed and demonstrated on the existing commodity multicore processor based systems. It may take some time for some of the previous works done on simulators (Xie and Loh [57], Chandra et al. [58], Rafique et al. [59], Suh et al. [60] and Hsu et al. [61]) to become applicable on real systems. We used machine learning techniques to develop the models by capturing the knowledge about the interactions of the applications and the processor architecture. The focus of studies have been on interactions of programs related with processor memory hierarchy resources, which are shared among the cores present on multicore processors. The use of

machine learning requires training the algorithms to synthesize the models, on the other hand some of the analytical models proposed in previous works by Chandra et al. [58] and Fedorova et al. [2] are fairly involved for application in real systems. The methodologies and mechanisms presented in the thesis do not require specialized support from hardware as proposed in some of the previous works by Xie and Loh [57], Chandra et al. [58], Rafique et al. [59], Suh et al. [60], Hsu et al. [61] and Qureshi and Patt [62]. The work also does not require any modifications or recompilations of the applications. We provide experimental evidence that the developed methodologies using machine learning techniques can be utilized to achieve performance gains. The methodologies developed as part of our work create further research possibilities. Fellow researchers can use these methodologies as initial point, for using, improving and extending the ideas.

#### 1.4 Organization of the Thesis

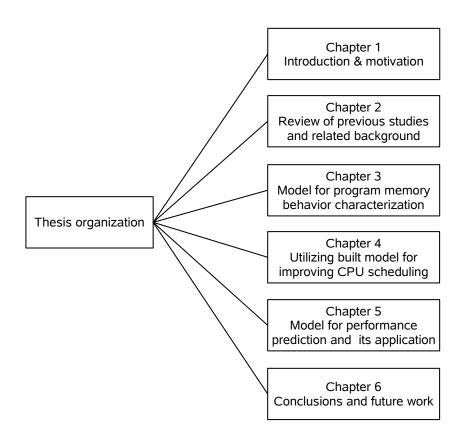

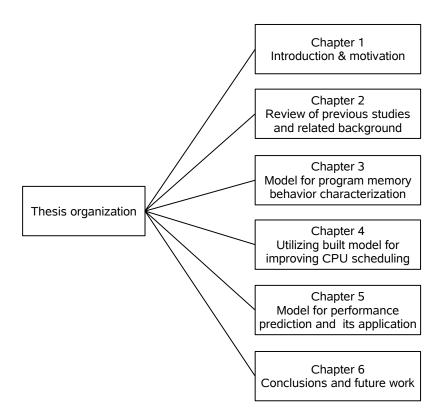

The thesis is organized into six chapters as mentioned below. Though the chapters are related with each other, we tried to present each chapter in self-contained manner to the extent possible, to ease the sequential reading of the thesis document. Thesis organization is also shown in figure 1.3.

- Chapter 1: Introduction. The chapter gives an overview of evolution of processor architecture and associated performance studies, which provided the motivation behind the work carried out in the thesis. It also mentions the research objectives of the work.

- Chapter 2: Review of Performance Studies and Related Background. This chapter provides the review of the previous studies related with performance issues of multicore based computing systems, with specific emphasis on sharing of processor memory hierarchy resources among the cores present on the processors. It also gives an overview of machine learning and some of its applications in computer systems research.

- Chapter 3: Characterization of Program Memory Behavior. This chapter presents the methodology for characterizing the program memory behavior on multicore processors. The chapter also provides brief description of machine learning algorithms as well as experimental platforms used in the study. It describes the program attributes and the experimental method to gather the data from a multicore processor based platform to generate the training data-set. It also describes the

Figure 1.3: Thesis organization.

prediction accuracy results of the trained model and its transferability over other experimental multicore platform.

- Chapter 4: Improving Process Scheduling. This chapter describes a meta-scheduler as an example application of the model built for program memory behavior characterization. It also provides the results on improvement in performance, observed with the meta-scheduler along with details of experimental setup.

- Chapter 5: Performance Prediction. This chapter describes the methodology to build model for performance prediction on multicore processors along with experimental setup and results. It includes the proposed solo-run program attributes, which the model takes as inputs to predict the concurrent-run performance. It also describes the prospective application of the model (built to predict concurrent-run performance) for simulation of multicores.

- Chapter 6: Conclusions and Future Work. This chapter summarizes the major contributions of the work and mentions the observations. It also highlights the future research directions.

Overall the thesis covers the modeling of the performance aspects of multicore processors with focus on sharing of processor memory hierarchy resources among the cores present on the multicore processors. The models were built by training the machine learning algorithms. The applicative aspects of the research reported in the thesis are reflected in the prospective use of the developed models for – (i) improving process scheduling on multicores and (ii) simulation of multicores.

### Chapter 2

# Review of Performance Studies and Related Background

This chapter presents review of relevant literature on performance studies accompanied with shift towards multicore architecture. The chapter is organized as follows: In section 2.1, we begin with the description of the studies related with shared memory hierarchy resources present on multicore processors. The work done in this thesis uses machine learning techniques to synthesize the models. In section 2.2, we provide an overview of machine learning and its applications in computer systems research. Section 2.3 describes the work related to performance prediction studies on multicore processors followed by conclusions.

# 2.1 Shared Memory Hierarchy Related Studies

This section describes previous works related with management of shared caches on multithreaded and multicore processors. The various solutions proposed by researchers to manage the interference among co-running programs using shared caches on multicore and multithreaded processors mostly fall into two kinds of solutions:

- Hardware based solutions

- Software based solutions

Both solutions in general require knowledge about the memory behavior especially the shared last level (e.g. level-2) cache related characteristics of the programs running on the processor. Hardware based solutions propose extra

support from the processor hardware. Software based solutions include scheduling by operating systems and adaptations in memory management subsystem, which involve page coloring based techniques.

#### 2.1.1 Hardware Based Solutions

Among the hardware based solutions, Suh et al. [60] proposed memory monitoring scheme, which utilized a set of novel hardware counters. The counters provide the marginal gain in the cache hits as the size of the cache is increased. The scheme described in the work uses the counters, to get an accurate estimate of the isolated miss-rates of each process as a function of cache size under the standard LRU (Least Recently Used) replacement policy. Such information can be used to schedule jobs or to partition the cache to minimize the overall miss-rate. Unlike this work, our work does not require any new hardware counters and relies on the counters already available on existing commodity multicore processors.

In a later work Suh et al. [63] proposed a dynamic cache partitioning method for minimizing the overall miss rate and improving IPC (Instructions Per Cycle). The scheme uses a set of on-line counters to estimate gain or loss to each process in terms of the number of cache misses observed with different cache allocations. It changes the cache allocation so that more needy processes can get more cache space. This method requires a new cache replacement policy in place of the LRU replacement policy currently used in systems. The work was done on simulator. It requires changes in the hardware.

Kim et al. [64] studied fairness in cache sharing between threads in a chip multiprocessor (CMP) architecture. They evaluated cache fairness metrics for their correlation with the execution-time fairness. Execution-time fairness is defined as how uniform the execution times of co-scheduled threads are changed, where each change is relative to the execution time of the same thread for its solo-run. The work also proposed L2 (level-2) cache partitioning algorithms to be implemented in hardware to optimize fairness. They observed  $4 \times$  improvement in fairness and 15% increase in the throughput (combined instructions per cycle) with fair caching algorithms, compared to a non-partitioned shared cache.

Chandra et al. [58] studied the impact of L2 cache sharing among the corunning threads on a chip multiprocessor architecture. They proposed performance models to predict the impact of cache sharing on co-scheduled threads. The input to the models is the isolated L2 cache stack distance or circular

sequence profile of each thread. Stack distance profile of an application is a compact summary of its cache-line reuse patterns. The models give an estimate of the number of additional L2 misses caused by sharing, compared to solo-run of the thread (i.e. without sharing the L2 cache with other co-runner). The study used a cycle-accurate simulator for a dual-core CMP architecture. The proposed models are fairly involved for implementation in hardware.

Hsu et al. [61] discussed various cache policies for chip multiprocessors. Cache policies were named according to the target to be achieved, like Communist cache policies for equal performance target and Utilitarian cache policies for overall performance target and the most common current model of a free-for-all cache as Capitalist policy. They used analytical models and behavioral cache simulation and observed that thread-aware cache resource allocation mechanism is required for CMPs.

Qureshi and Patt [62] proposed a utility based cache partitioning scheme. In this scheme the share of the cache received by an application is proportional to the utility rather than its demand. The scheme uses Utility Monitor (UMON) a special kind of counters implemented in hardware. We discuss about the performance prediction part of this work in section 2.3.

Rafique et al. [59] proposed architectural support for chip multiprocessors that enables operating system (OS) level cache management. The proposed scheme consists of three components: a hardware cache quota enforcement mechanism, an OS interface and a set of OS-level policies for changing the quotas. The hardware mechanism enforces OS-specified, cache quotas in shared lower level caches for each sharing entity. The OS can provide various cache management policies by manipulating the quotas via the quota specification interface. Thus the proposed hardware based cache quota system, can be used by operating system to use different policies for different applications in order to improve the overall performance in chip multiprocessors.

Chang and Sohi [65] proposed Cooperative Cache Partitioning (CCP) to allocate cache resources among concurrently running threads on chip multiprocessors. The proposed scheme uses multiple time-sharing partitions. They integrated the proposed cache partitioning scheme with cooperative caching [66] for chip multiprocessors. The work was done on simulator for a 4-core chip multiprocessor. Cooperative caching [66] tries to reduce the number of off-chip accesses by combining the strengths of private and shared caches adaptively. It requires additional modifications in existing cache replacement policy and coherence protocol.

Zhao et al. [67] investigated mechanisms for fine-grain monitoring of the use

of shared cache resources on chip-multiprocessors. They proposed the cache monitoring architecture named CacheScouts, consisting of tagging (software guided monitoring IDs), and sampling mechanisms (set sampling) to achieve shared cache monitoring on per application basis. The study was performed on a cache hierarchy simulator called CASPER [68]. They also mentioned about the use of CacheScouts [67] in operating systems and virtual machine monitors for – characterizing execution profiles, optimizing scheduling for performance management, providing quality of service (QoS) and metering for chargeback. The proposed scheme needs to be implemented in hardware.

Xie and Loh [57] proposed a new classification algorithm for determining the personalities of the programs with respect to their cache sharing behavior. The proposed algorithm needs to be implemented in hardware, to help the partitioning of the cache between the running programs to reduce the shared cache interference caused by co-running programs on multicore processors. The main focus of the work was to help in partitioning the caches between running programs, though the results can also be utilized for scheduling the programs. This work was performed on simulator for dual-core processor.

Srikantaiah et al. [69] proposed an operating system directed integrated processor-cache partitioning for chip multiprocessors. The scheme partitions both the available processors and the shared cache in a chip multiprocessor among running applications. The scheme uses a regression based model to predict the behavior of applications to find the most suitable processor and L2 cache partitions. In the proposed scheme cache partitioning is done by allocating one cache partition to each processor-set (processor partition), thereby encouraging constructive sharing among threads of the same application and alleviating the impact of interference among different applications in the cache. The proposed partitioning approach is iterative, that involves partitioning of processors and cache in a series of iterations. The processor partitioning performed in one iteration influences the cache partitions in the same iteration and the cache partition at the end of the current iteration influences the processor partitioning in the following iteration. They used Simics full system simulator [70] in the study. The scheme involves changes in both hardware as well as operating systems.

The solutions requiring modifications in the processor hardware may need time to get implemented and available in commodity processors. The approach taken in our work does not require any changes in cache replacement policies or any other components of the existing commodity hardware.

#### 2.1.2 Software Based Solutions

Among the software based solutions, Bulpin and Pratt [34] proposed process scheduling heuristics for hyperthreaded Pentium 4 processor to avoid the pathological combinations of workloads, which can give a poor system throughput. The hyperthreads introduced by hyperthreading technology of Intel are abstracted by the hardware as logical processors. They observed that the existing operating systems process scheduling does not take account of the particular resource requirements of the individual threads, which can cause the sub-optimal schedules to take place. In their work multiple linear regression was used to model the speed-up ratio of a program in solo-run as compared to paired-run with co-running sibling thread. The off-line trained model was used to change the dynamic priority of a process in linux process scheduler. It was done so that a runnable process could be given a higher dynamic priority if it is likely to perform well with the process currently running on the other logical processor. In this scheme the kernel need to keep a record of the estimated system-speedups of pairs of processes. Their work demonstrated the scheduling heuristics using the standard linux-2.4 scheduler – a single-queue dynamic priority based scheduler where priority is calculated for each runnable task at each rescheduling point. In the next version, linux-2.6 introduced changes in the process scheduler which maintains a run queue per processor. The independence of scheduling between the processors complicates coordination of pairs of tasks. The investigation of the application of the proposed heuristics for linux-2.6 was part of their future work.

Fedorova et al. [2] proposed an L2-cache conscious scheduling algorithm for efficient utilization of the shared last level (L2) cache on multithreaded chip multiprocessors. Their OS scheduling algorithm is based on the balance-set principle proposed by Denning [71]. Balance-set scheduling involves scheduling the runnable threads into subsets or groups, such that the combined working set of each group fits in the cache. By making sure that the working set of each scheduled group fits in the cache, the proposed algorithm reduces cache misses. The work involves use of estimated cache miss ratios for each group of threads as metric for making scheduling decisions. The model [72] used in the work for estimating cache miss ratios is based on cache model for single-threaded workloads developed by Berg and Hagersten [73]. The cache miss ratios of multithreaded workloads estimated by model were within 17% of the actual values, on average. Estimation of cache miss ratios by the Berg-Hagersten model requires monitoring of memory re-use patterns of the threads. Implementation

of such monitoring requires to capture a sample of memory locations that a thread references and then to record how often those locations are reused. This approach is expensive for use in a real system, because it needs handling frequent processor traps. Fedorova et al. performed the study on simulator for chip multithreaded processor using benchmarks from the SPEC cpu2000 suite [74]. They observed that the L2-cache conscious scheduling algorithm had the potential to reduce the L2 cache miss ratios by 25-37%, thereby yielding a performance improvement of 27-45%.