# System Design and Prototyping of the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC

A thesis submitted for the degree of

**Doctor of Philosophy**

In

**Electronics Science and Engineering**

by

#### PIYUSH KUMAR

(19PHPE04)

Centre for Advanced Studies in Electronics Science and Technology

School of Physics

University of Hyderabad

Hyderabad, Telangana- 500046, India

March-2024

#### University of Hyderabad Hyderabad, Telangana- 500046, India

#### Declaration

I, PIYUSH KUMAR, hereby declare that this thesis entitled "System Design and Prototyping of the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC" submitted to the University of Hyderabad, Hyderabad, India for the award of degree of Philosophy in Electronics Science and Engineering is a record of original research work carried out by me under the supervision of Dr. Bhawna Gomber, Center for Advanced Studies in Electronics Science and Engineering and Technology (CASEST), School of Physics, University of Hyderabad. To the best of my knowledge, the thesis is not submitted for any degree in any University or Institute.

Date: 22 March 2024

Place: Hyderabod, India

Mr. PIYUSH KUMAR

Reg. No. 19PHPE04

Veget Keun

#### University of Hyderabad Hyderabad, Telangana- 500046, India

#### Certificate

(For Ph.D. Dissertation)

This is to certify that the thesis entitled "System Design and Prototyping of the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC" submitted by "Mr. PIYUSH KUMAR" bearing the registration number 19PHPE04 in partial fulfillment of the requirements for the award of Doctor of Philosophy in Electronics Science and Engineering, is submitted to the Centre for Advanced Studies in Electronics Science and Technology (CASEST), School of Physics, University of Hyderabad, Hyderabad, India is a bonafide work carried out by him under my supervision and guidance.

This thesis is free from plagiarism and has not been submitted previously in part or in full to this or any other University or Institution for the award of any degree or diploma.

Further, the undertaken work has the following publications, talks, and poster presentations before submission of the thesis for adjudication and has produced evidence for the same in the form of an acceptance letter or the reprint in the area of his research.

#### Journal publications:

- P. Kumar and B. Gomber, "System Design and Prototyping for the CMS Level-1 Trigger at the High-Luminosity LHC," in IEEE Transactions on Nuclear Science, vol. 70, no. 6, pp. 1075-1082, June 2023, doi: 10.1109/TNS.2023.3247510.

- 2. **P. Kumar** and B. Gomber, "The CMS Level-1 Calorimeter Trigger for the HL-LHC", Instruments, vol. 6, no. 4, p. 64, Oct. 2022, doi: 10.3390/instruments6040064.

#### Conference proceedings:

- 1. **Piyush Kumar**. "The Particle Flow Algorithm in the Phase II Upgrade of the CMS Level-1 Trigger". PoS, EPS-HEP2021:771, 202.

- 2. **Piyush Kumar**, and Bhawna Gomber on Behalf of the CMS Collaboration, "Firmware Development for the Phase-2 Upgrade of the Calorimeter L1 Trigger for the CMS Detector," in Springer Nature (under review).

#### Talk in Workshops and Conferences:

- 1. "The Calorimeter Trigger Slice Test" at Level-1 Trigger Workshop @CERN (online), 27-30 April 2022, CERN, Geneva, Switzerland.

- 2. "System Design and Prototyping for the CMS Level-1 Trigger at the High-Luminosity LHC", 23rd Virtual IEEE Real Time Conference, Online, 1-5, August 2022.

- "Firmware Development for the Phase-2 Upgrade of the Calorimeter L1 Trigger for the CMS Detector", XXV DAE-BRNS High Energy Physics Symposium 2022, 12-16, December 2022, IISER Mohali, Mohali, India.

- 4. "System Design and Prototyping for the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC", CMS General Meeting: WGM 589, CERN, Geneva, Switzerland.

- 5. "Calorimeter Trigger Slice Test Results and Plans", 11-15, September 2023, Level-1 Trigger Workshop @Athens, Athens, Greece.

#### **Poster Presentations:**

- 1. "Calorimeter Level-1 Trigger Upgrade for the CMS Detector at the HL-LHC", XXIV DAE-BRNS High Energy Physics Symposium, 14-28 December 2020, online.

- "The Particle Flow Algorithm in the Phase II Upgrade of the CMS Level-1 Trigger", The European Physical Society Conference on High Energy Physics 2021, Online, 26-30 July 2021.

- "The CMS Level-1 Calorimeter Trigger for the HL-LHC", CALOR 2022 19th International Conference on Calorimetry in Particle Physics, 16-20 May 2022, University of Sussex, UK.

- 4. "The Calorimeter L1 Trigger for the HL-LHC", 12th India-Japan Science and Technology Seminar, International Conference on Frontier Areas of Science and Technology (ICFAST-2022), 09-10 September 2022, University of Hyderabad, Hyderabad, India.

- 5. "System Design and Prototyping for the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC", CMS Upgrade days at CERN, 06-08 February 2023, CERN, Geneva, Switzerland (Won the best poster award).

- 6. "System Design and Prototyping of the CMS Level-1 Calorimeter Trigger at the High-Luminosity LHC", 13th LHC students poster session, 27 November 2023, CERN, Geneva, Switzerland.

Further, the student has passed the following courses towards fulfillment of course work requirement for Ph.D.

| S. No. | Course Code | Name                                                             | Credits | Pass/Fail |

|--------|-------------|------------------------------------------------------------------|---------|-----------|

| 1      | CS478       | Pattern Recognition                                              | 3       | Pass      |

| 2      | CS490       | Machine Learning                                                 | 3       | Pass      |

| 3      | PE708       | Research Methodology                                             | 4       | Pass      |

| 4      | PE716       | High Speed VLSI and System On Chip:<br>Design and Implementation | 4       | Pass      |

Dr. Bhawna Gomber Supervisor

Dr. Bhawna Gomber Assistant Professor CASEST, School of Physics University of Hyderabad Hyderabad-500046, Telangana.

CASEST, School of Physics

CASEST, School of Physics

HEAD, CASEST

(Centre for Advanced Studies in Electronics Science & Technology) School of Physics University of Hyderabad-500 046.

Dean

School of Physics DEAN

School of Physics **University** of Hyderabad HYDERABAD - 500 046

## **ABSTRACT**

The High-Luminosity LHC (HL-LHC) project offers a very ambitious physics program that includes high-precision measurements of the Standard Model (SM) and the searches for new physics beyond the SM (BSM). The efficient data collection and precise events reconstruction in the harsh environment of 200 proton-proton interactions per bunch crossing are vital for achieving the success of the HL-LHC program. To fulfill these requirements, the CMS experiment plans to build and install completely new data acquisition (DAQ) and trigger systems during the so-called CMS Phase-2 upgrade. The Phase-2 CMS Level-1 calorimeter trigger system will handle the enormous detector input data bandwidth of 75 Tbps and is desired to complete the single event processing within 12.5  $\mu$ s. For this purpose, CMS plans to replace the Phase-1  $\mu$ TCA-based processor boards and crates with an ATCA form factor. Each ATCA board will host Xilinx Ultra-Scale+ family FPGA that supports over a hundred high-speed optical links at 25 Gbps, capable of meeting the high bandwidth and processing requirements of the HL-LHC. Along with the advancement in hardware, the Level-1 trigger system will employ highly modular, flexible, and adequately sophisticated algorithms currently possible only in offline reconstruction, such as a particle-flow algorithm. The modular and flexible architecture will help to address the HL-LHC physics requirements. In this thesis, we will discuss the system design, prototyping, and algorithms being developed for the Phase-2 Level-1 Calorimeter trigger system.

### Acknowledgements

First and foremost, I would like to express my deepest gratitude toward my Ph.D. supervisor **Dr. Bhanwa Gomber**. This Ph.D. journey would not have been possible without your immense support and mentorship. Thank you for opening a new world to me by allowing me to work in the CMS collaboration and helping me grow as a better person, personally and professionally. Your passion for the work still inspires me to push myself more. I could not have imagined having a better supervisor and mentor in my Ph.D. journey.

I want to express my sincere gratitude to **Prof. Sridhara Dasu** and **Dr. Alexander** (Sascha) Savin from the University of Wisconsin for providing me with the opportunity to work on the Phase-2 Level-1 calorimeter trigger project. Thank you for providing me with financial and academic support for my one-year stay at CERN. Moreover, I want to thank Sascha for his continuous and tremendous support during my Ph.D. journey. I will always adore the wisdom I have received from him during my Ph.D.

I want to express my special gratitude toward my international collaborators, **Dr. Isobel Ojalvo**, **Dr. Varun Sharma**, **Ales Svetek**, **Luis Moreno**, **Kiran Kumar Das**, and **Dr. Alexander Zabi**. Their academic and technical support made this journey smooth and enjoyable.

I want to thank my Ph.D. review committee members, **Prof. S.L. Sabat**, **Prof. S. V. S. Nageswara Rao**, **Prof. G Rajaram**, and **Dr. Vijaya Shankara Rao**, for their insightful discussions and comments during doctorate review presentations. It gave me a broad research perspective and encouraged me to improve positively.

I want to express my sincere gratitude to Dean, School of Physics **Prof. K.C. James Raju**, and Head of CASEST **Prof. Prof. Ghanashyam Krishna** for providing the necessary facilities and an enjoyable working experience at the University.

I take this opportunity to thank **Dr. Bhawna Gomber**, **Prof. Guruswamy Rajaram**, **Prof. K.C.James Raju**, **Prof. M. Ghanashyam Krishna**, **Prof. S.V.S Nageswara Rao**, **Dr. Vijaya Sankara Rao**, and **Dr. Pratap Kollu** for their teaching and support during my coursework in my Ph.D. and M.Tech.

I want to express my profound appreciation to my colleague **Bisnupriya Sahu** for her constant and pristine support in my Ph.D. journey. Together with her, this Ph.D. journey was extremely enjoyable and memorable.

I am thankful to my colleagues Shriniketan, Shiva, Anil, Vinay, Ravi, Gnani, Chenna, and Rakesh. They made this journey memorable and enjoyable.

I want to express my special thanks to my mother Ms. Rekha Gupta, my father Mr. Vijay Kumar, and my maternal grandmother Ms. Parvati Gupta for encouraging me in my pursuits and inspiring me to follow my passion. Thank you for teaching me lessons of life that made me the person I am today.

I take this opportunity to especially thank my sister **Sneha Sahu** and brother **Vineet Gupta** for their constant support, love, and care throughout my life.

I take this opportunity to especially thank Mr. Antoni Jakubowski and Dr. Varun Sharma for their tremendous support and help for my smooth stay at CERN. I learned many new dimensions of life, which eventually helped me personally and professionally. I am also thankful to Kiran for guiding me during my stay at CERN.

I would also very much like to thank all the non-teaching staff of CASEST and the School of Physics, especially **Ravi Babu** sir for guiding me in all the administrative work.

Finally, I would like to thank and acknowledge the support for the fellowship from different funding agencies: the **University of Hyderabad**, the **SERB startup grant**, and the **IoE Grant**. I would also like to thank the University Institute of Eminence office for supporting me in giving a talk at the L1 trigger workshop in Athens, Greece.

## Contents

| D            | eclar  | ation     |                                                         | i            |

|--------------|--------|-----------|---------------------------------------------------------|--------------|

| C            | ertifi | cate      |                                                         | ii           |

| <b>A</b>     | bstra  | ıct       |                                                         | $\mathbf{v}$ |

| A            | ckno   | wledge    | ements                                                  | vi           |

| Li           | st of  | Figure    | es                                                      | xi           |

| Li           | st of  | Table     | S                                                       | xvi          |

| $\mathbf{A}$ | bbre   | viation   | ıs                                                      | xviii        |

| 1            | Inti   | roducti   | ion                                                     | 1            |

| _            | 1.1    |           | ture Review                                             |              |

|              | 1.2    |           | em Definition                                           |              |

|              | 1.3    |           | S Objective                                             |              |

|              | 1.4    | Propo     | sed Solution and Thesis Contribution                    | . 5          |

|              | 1.5    | _         | S Organization                                          |              |

|              |        | 1.5.1     | Chapter 1: Introduction                                 | . 7          |

|              |        | 1.5.2     | Chapter 2: The CMS experiment at the LHC-CERN           | . 8          |

|              |        | 1.5.3     | Chapter 3: Triggering in High Luminosity LHC            | . 8          |

|              |        | 1.5.4     | Chapter 4: Phase-2 Level-1 Calorimeter Trigger          | . 8          |

|              |        | 1.5.5     | Chapter 5: Calorimeter Trigger Algorithm                | . 8          |

|              |        | 1.5.6     | Chapter 6: Calorimeter Trigger Firmware and Prototyping | . 8          |

|              |        | 1.5.7     | Chapter 7: Summary, Conclusions, and Future Work        | . 9          |

| 2            | The    |           | experiment at the LHC-CERN                              | 10           |

|              | 2.1    |           | arge Hadron Collider                                    |              |

|              | 2.2    |           | Concept of Luminosity in Colliders                      |              |

|              | 2.3    |           | Compact Muon Solenoid (CMS) Experiment                  |              |

|              |        | 2.3.1     | CMS coordinate system                                   |              |

|              |        | 2.3.2     | Detector Layout and Salient Features                    |              |

|              |        | $2\ 3\ 3$ | Electromagnetic Calorimeter                             | 16           |

Contents

|   |            |        | 2.3.3.1 ECAL Layout                       | 16       |

|---|------------|--------|-------------------------------------------|----------|

|   |            | 2.3.4  | Hadronic Calorimeter                      |          |

|   |            | 2.3.5  | Solenoid Magnet, Tracker, and Muon System | 19       |

|   |            |        | 2.3.5.1 Solenoid Magnet                   |          |

|   |            |        | 2.3.5.2 Tracker                           |          |

|   |            |        | 2.3.5.3 Muon System                       | 22       |

|   |            | 2.3.6  | Triggering at the CMS                     | 23       |

|   |            |        | 2.3.6.1 Level-1 Trigger                   | 23       |

|   |            |        | 2.3.6.2 High Level Trigger                | 27       |

| 3 | Hig        | h Lum  | inosity LHC and Triggering in Phase-2     | 29       |

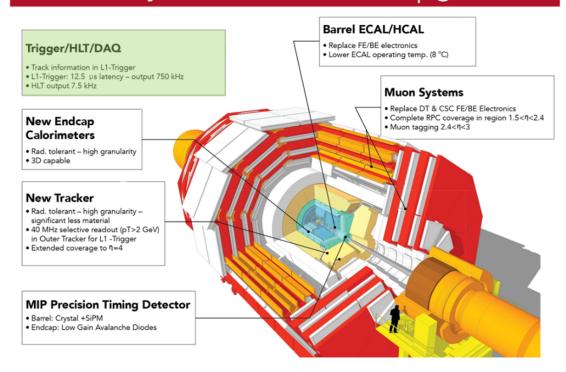

|   | 3.1        | Phase- | 2 Upgrade of the CMS Detector             | 30       |

|   |            | 3.1.1  | Pixel and Tracker                         | 30       |

|   |            | 3.1.2  | Muon system                               | 31       |

|   |            | 3.1.3  | Calorimeter                               | 32       |

|   |            | 3.1.4  | Data Acquisition (DAQ)                    | 34       |

|   |            | 3.1.5  | Level-1 Trigger                           | 36       |

| 4 | Pha        |        |                                           | 39       |

|   | 4.1        | -      | sed Solution and Architecture             |          |

|   | 4.2        | Hardw  | rare Infrastructure of Phase-2            |          |

|   |            | 4.2.1  |                                           | 41       |

|   |            | 4.2.2  |                                           | 43       |

|   |            | 4.2.3  | CMS Standard Protocol (CSP)               |          |

|   | 4.3        |        |                                           | 46       |

|   | 4.4        |        | thm and Firmware Design Flow              |          |

|   | 4.5        |        | 1                                         | 48       |

|   | 4.6        |        | 31 0                                      | 49       |

|   |            | 4.6.1  | Very high-throughput                      |          |

|   |            | 4.6.2  |                                           | 49       |

|   |            | 4.6.3  | Latency                                   |          |

|   |            |        | Utilization                               |          |

|   |            | 4.6.5  | Input and Output bit-width constraints    | 50       |

| 5 |            |        | 88 8                                      | 52       |

|   | 5.1        |        | •                                         | 52       |

|   | 5.2        |        |                                           | 53       |

|   | 5.3        |        | 00 ( )                                    | 54       |

|   |            | 5.3.1  |                                           | 56       |

|   |            | 5.3.2  |                                           | 33       |

|   |            |        |                                           | 36       |

|   |            |        |                                           | 74       |

|   | <b>.</b> . | т      |                                           | 79       |

|   | 5.4        |        |                                           | 34       |

|   |            | 5.4.1  |                                           | 34       |

|   |            |        | 0                                         | 38<br>90 |

|   |            |        | 0.4 1 2 162                               | 41 I     |

*Contents* x

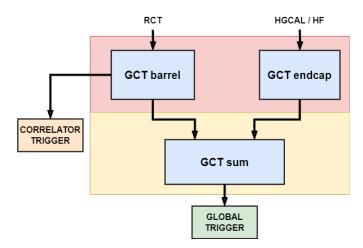

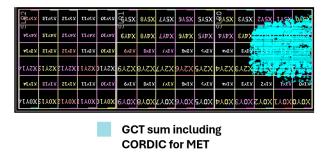

| 5.4.3 Layer-3: GCT Sum  5.5 Conclusions  6 Calorimeter Trigger Firmware, and Prototyping  6.1 Calorimeter Trigger Prototype and Test Setup  6.2 Prototyping Regional Calorimeter Trigger  6.2.1 RCT v1.0  6.2.2 RCT v2.0  6.3 Prototyping Global Calorimeter Trigger  6.3.1 Prototyping GCT Barrel  6.3.2 Prototyping GCT endcap  6.3.3 Prototyping GCT sum  6.4 Prototyping Barrel Calorimeter Trigger  6.4.1 RCT v1.0 to GCT (MET) algorithm  6.4.2 RCT v2.0 and GCT Barrel algorithm  6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions | 93  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6 Calorimeter Trigger Firmware, and Prototyping 6.1 Calorimeter Trigger Prototype and Test Setup 6.2 Prototyping Regional Calorimeter Trigger 6.2.1 RCT v1.0 6.2.2 RCT v2.0 6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions  A Clock Domain Crossing                             |     |

| 6.1 Calorimeter Trigger Prototype and Test Setup 6.2 Prototyping Regional Calorimeter Trigger 6.2.1 RCT v1.0 6.2.2 RCT v2.0 6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions  A Clock Domain Crossing                                                                             | 105 |

| 6.2 Prototyping Regional Calorimeter Trigger 6.2.1 RCT v1.0 6.2.2 RCT v2.0 6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions  A Clock Domain Crossing                                                                                                                              | 106 |

| 6.2.1 RCT v1.0 6.2.2 RCT v2.0 6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions                                                                                                                                                                                                    | 106 |

| 6.2.2 RCT v2.0  6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum  6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions                                                                                                                                                                                                                 | 108 |

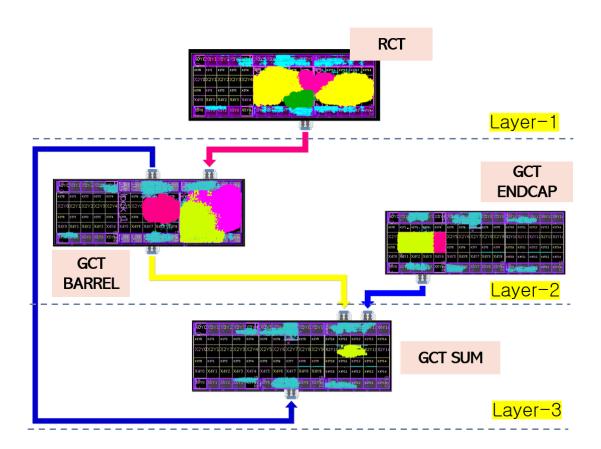

| 6.3 Prototyping Global Calorimeter Trigger 6.3.1 Prototyping GCT Barrel 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions  A Clock Domain Crossing                                                                                                                                                                                                         | 108 |

| 6.3.1 Prototyping GCT Barrel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110 |

| 6.3.2 Prototyping GCT endcap 6.3.3 Prototyping GCT sum 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System  7 Summary and Conclusions  A Clock Domain Crossing                                                                                                                                                                                                                                                                                 | 111 |

| 6.3.3 Prototyping GCT sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 111 |

| 6.4 Prototyping Barrel Calorimeter Trigger 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System 7 Summary and Conclusions  A Clock Domain Crossing                                                                                                                                                                                                                                                                                                                                         | 113 |

| 6.4.1 RCT v1.0 to GCT (MET) algorithm 6.4.2 RCT v2.0 and GCT Barrel algorithm 6.5 Prototyping Calorimeter Trigger System                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 6.4.2 RCT v2.0 and GCT Barrel algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 115 |

| 6.4.2 RCT v2.0 and GCT Barrel algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 115 |

| 7 Summary and Conclusions  A Clock Domain Crossing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| A Clock Domain Crossing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 117 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 120 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 129 |

## List of Figures

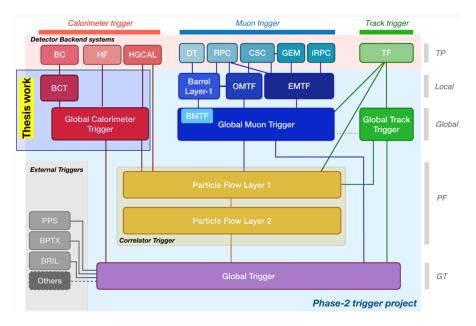

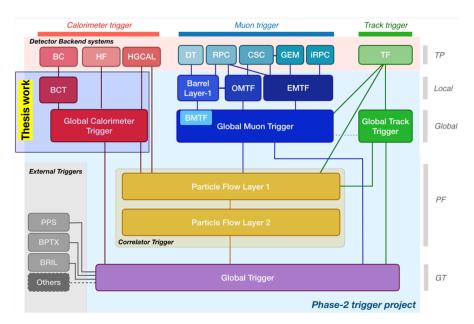

| 1.1  | CMS Phase-2 Level-1 trigger system architecture comprising three trigger sub-systems: calorimeter, muon, and track [6]. The correlator trigger is also included in the L1 trigger architecture. The thesis work entirely focuses on the design and prototyping of the calorimeter trigger highlighted |                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.2  | in the box                                                                                                                                                                                                                                                                                            | 4<br>7          |

| 1.3  | Two level architecture of the Phase-2 Level-1 calorimeter trigger                                                                                                                                                                                                                                     | 7               |

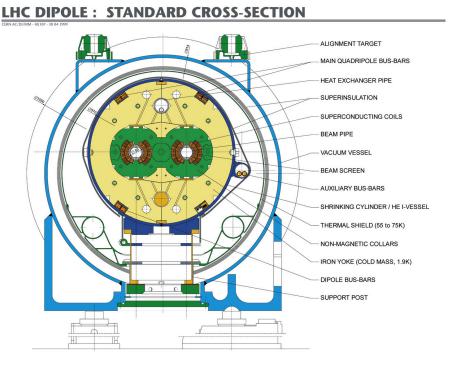

| 2.1  | Cross-section of the LHC dipole [1].                                                                                                                                                                                                                                                                  | 11              |

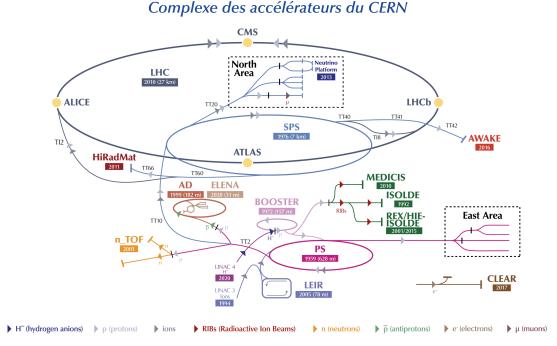

| 2.2  | CERN injector chain and LHC[1]                                                                                                                                                                                                                                                                        | 12              |

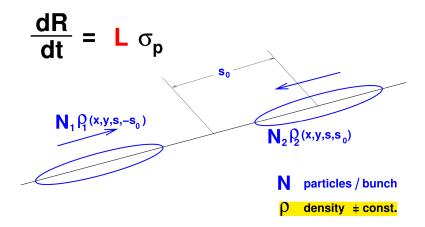

| 2.3  | Graphical representation of two colliding beams [16]                                                                                                                                                                                                                                                  | 13              |

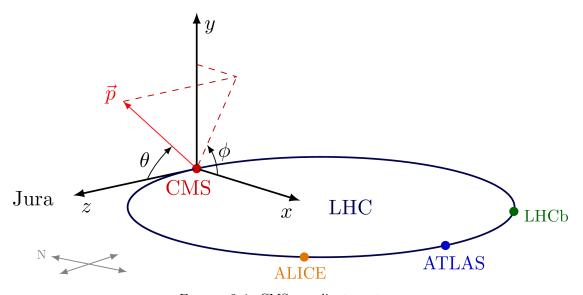

| 2.4  | CMS coordinate system                                                                                                                                                                                                                                                                                 | 14              |

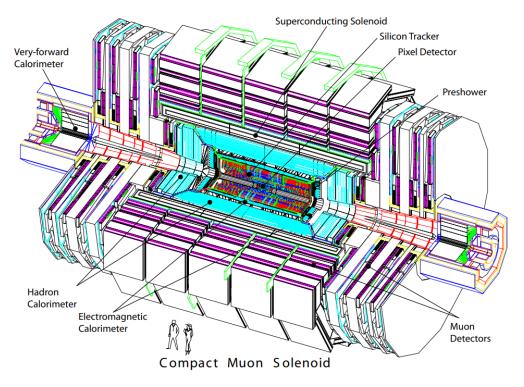

| 2.5  | CMS detector [2]                                                                                                                                                                                                                                                                                      | 15              |

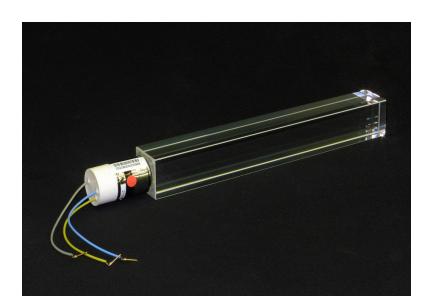

| 2.6  | $PbWO_4$ crystal with APD photodetector attached [2]                                                                                                                                                                                                                                                  | 17              |

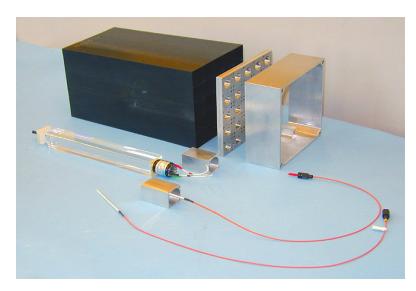

| 2.7  | Alveolar, Interface Plate, Housing, Optical Fibre Insert, Crystal and VPT                                                                                                                                                                                                                             |                 |

|      | and End-Stop of the CMS ECAL Endcap (EE) [20]                                                                                                                                                                                                                                                         | 17              |

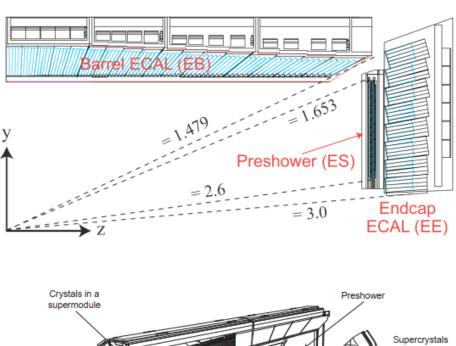

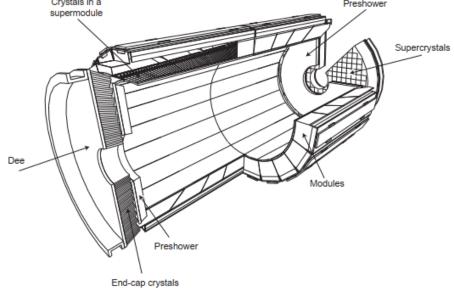

| 2.8  | Longitudinal (top) and 3D (bottom) view of the CMS calorimeter system                                                                                                                                                                                                                                 |                 |

|      |                                                                                                                                                                                                                                                                                                       | 18              |

| 2.9  | Schematic diagram of the HCAL elements in the CMS, including the                                                                                                                                                                                                                                      |                 |

|      | barrel hadronic (HB), the endcap region (HE), the tail catcher beyond                                                                                                                                                                                                                                 |                 |

|      | the magnet (HO), and the forward hadronic (HF) [2]                                                                                                                                                                                                                                                    | 20              |

| 2.10 | 1 0                                                                                                                                                                                                                                                                                                   |                 |

|      | tector module, whereas the double lines point to the back-to-back modules                                                                                                                                                                                                                             | 0.1             |

| 0.11 |                                                                                                                                                                                                                                                                                                       | 21              |

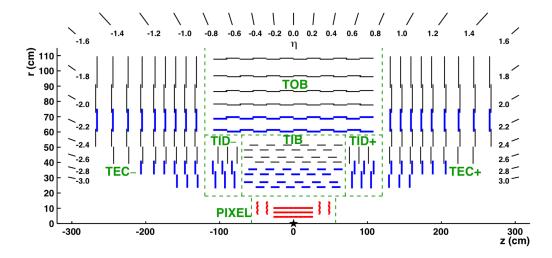

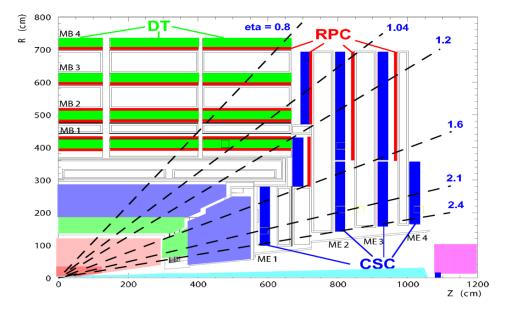

| 2.11 | One quadrant layout of the muon detector in the r - z plane depicting the                                                                                                                                                                                                                             | 20              |

| 0 10 | placement of muon sub-detectors viz. DT, RPC, and CSC. [21] Schematic of CMS trigger system implemented in two-level: first is the                                                                                                                                                                    | 22              |

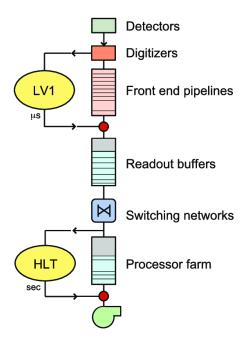

| 2.12 | Level-1 trigger (LV1) based on custom-designed FPGA boards, and sec-                                                                                                                                                                                                                                  |                 |

|      | ond is the high-level trigger (HLT) based on processor farm                                                                                                                                                                                                                                           | 23              |

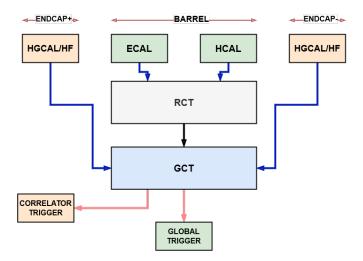

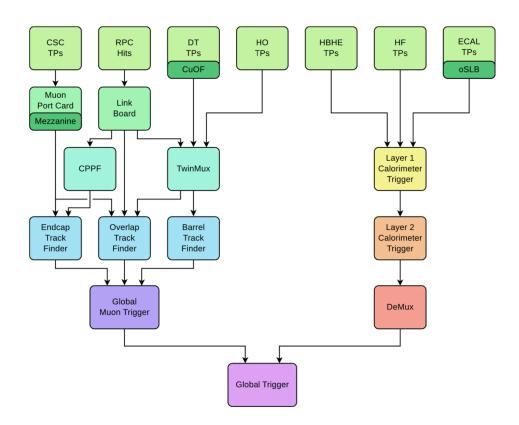

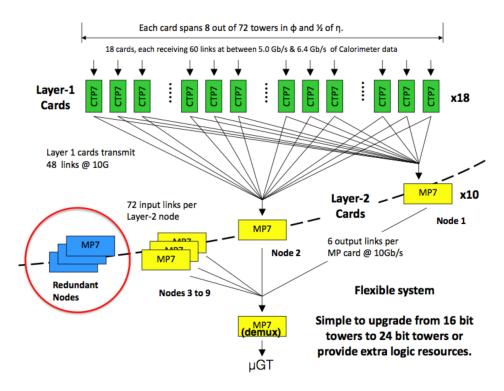

| 2 13 | CMS Phase-1 Level-1 trigger architecture [22]                                                                                                                                                                                                                                                         | $\frac{23}{24}$ |

|      | The Phase-1 Level-1 trigger are intecesting [22].  The Phase-1 Level-1 calorimeter trigger. The boards are organized in two                                                                                                                                                                           | 47              |

| 2.17 | layers. Layer-1 comprises 18 CTP7 boards receiving a total of 1152 input                                                                                                                                                                                                                              |                 |

|      | links. Each board sends 48 output links (4 links per bunch-crossing) to                                                                                                                                                                                                                               |                 |

|      | the MP7 board (via a patch panel), which are organized in TM9 mode                                                                                                                                                                                                                                    |                 |

|      | with three redundant or spare boards. Each MP7 board receives 72 input                                                                                                                                                                                                                                |                 |

|      | links and sends six output links to the GT [8]                                                                                                                                                                                                                                                        | 25              |

List of Figures xii

|     | The VT892 $\mu$ TCA crate from Vadatech. The ventilation cavities for the top-bottom cooling are apparently visible. The dual power modules (PMs) are located on the left of the crate. The dual $\mu$ TCA Carrier Hubs (MCHs) cards are placed in the center. The center top MCH slot is occupied with a custom "AMC13" module                                                                                                                                                                    |   | 26<br>27                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------|

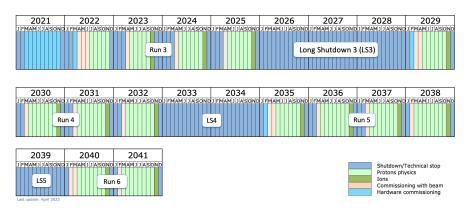

| 3.1 | The LHC timeline and its advancement to the HL-LHC (May 2029 to                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 20                              |

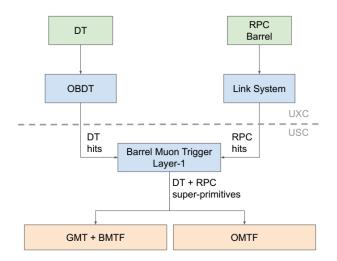

| 3.2 | October 2038) after Long-Shutdown 3 [27]                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | <ul><li>29</li><li>31</li></ul> |

| 3.3 | Barrel muon trigger primitive generation architecture. The DT information is processed via the onboard DT frontend system and ultimately forwarded to the backend barrel muon trigger layer-1 (BMTL1). The barrel RPC hits are transferred via the link system. The BMTL1 performs the clustering of the RPC hits, constructs the DT trigger segments, and merges both collections into super-primitives. The BMTL1 trigger primitive outputs are sent to the Overlap Muon Track Finder (OMTF) and |   |                                 |

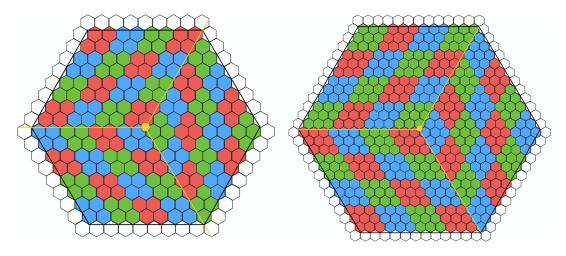

| 3.4 | Barrel Muon Track Finder (BMTF) via the high-speed optical links [26]. Illustration of the grouping of sensor cells in three-fold diamond pattern on hexagonal 8-inch silicon wafer. Arrangement of large sensor cell (1.18)                                                                                                                                                                                                                                                                       | • | 32                              |

|     | $cm^2$ ) is shown in left and smaller cell $(0.52 \ cm^2)$ in the right [9]                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 33                              |

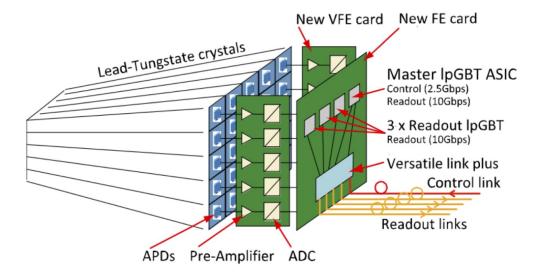

| 3.5 | ECAL Phase-2 front-end readout scheme [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 34                              |

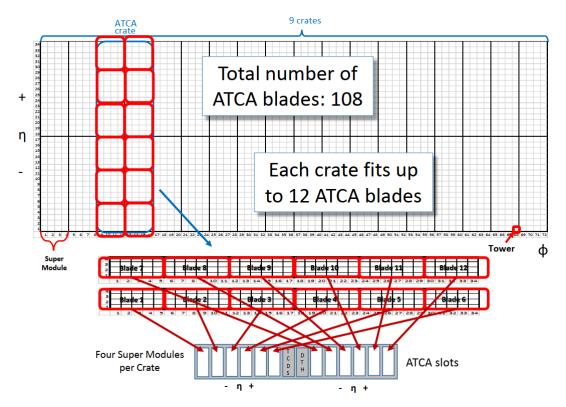

| 3.6 | Mapping of the BCP crate with the barrel ECAL [31]                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 35                              |

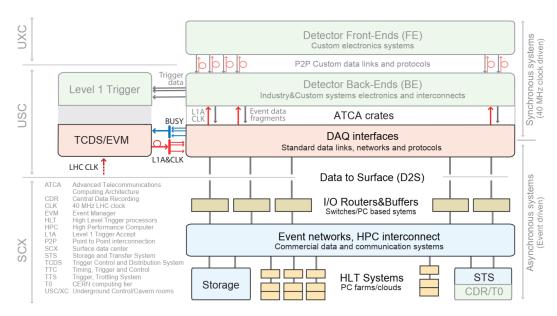

| 3.7 | Asynchronous and synchronous interface of the CMS Phase-2 DAQ system [32]                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 36                              |

| 3.8 | Graphical representation of Phase-2 DAQ system [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 37                              |

| 3.9 | CMS Phase-2 L1 trigger system comprises three trigger sub-systems: calorimeter, muon, and tracker [26]                                                                                                                                                                                                                                                                                                                                                                                             |   | 38                              |

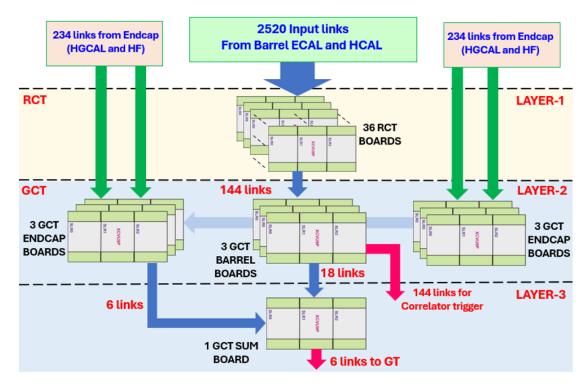

| 4.1 | Two-level and three layers architecture of the calorimeter trigger using APx boards                                                                                                                                                                                                                                                                                                                                                                                                                |   | 40                              |

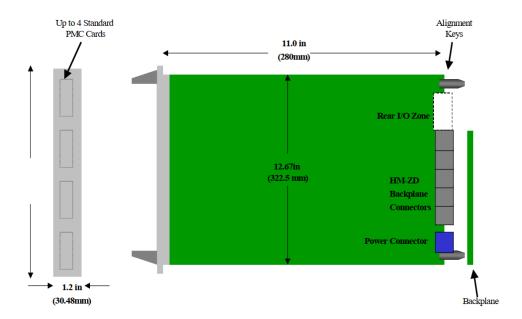

| 4.2 | ATCA board specifications [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 42                              |

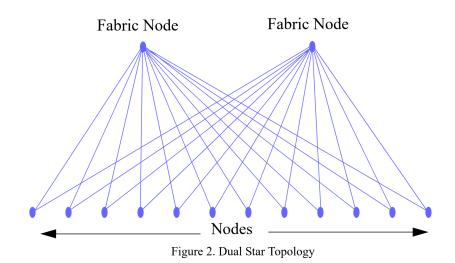

| 4.3 | Dual Star connection topology [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 42                              |

| 4.4 | CMS dual star backplane connection topology. Each of the two hub                                                                                                                                                                                                                                                                                                                                                                                                                                   | • | 12                              |

| 1.1 | boards are connected with the node board in "star" convention [26]                                                                                                                                                                                                                                                                                                                                                                                                                                 | _ | 43                              |

| 4.5 | APd1 board with the XCVU9P FPGA beneath the heatsink                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 44                              |

| 4.6 | A first DTH prototype in a test chassis. The left side of the diagram                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                 |

|     | represents the front panel of the DTH board. Two black heatsinks cover the TCDS (bottom) and DAQ (top) FPGAs. Connectivity to central                                                                                                                                                                                                                                                                                                                                                              |   |                                 |

|     | services is supplied via front-panel QSFPs (for the D2S network) and                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                 |

|     | SFPs (for TCDS2). Connections to the node board occur via Firefly optics and backplane connectors, assigning the front-panel optics for sub-                                                                                                                                                                                                                                                                                                                                                       |   |                                 |

|     | system data [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ | 47                              |

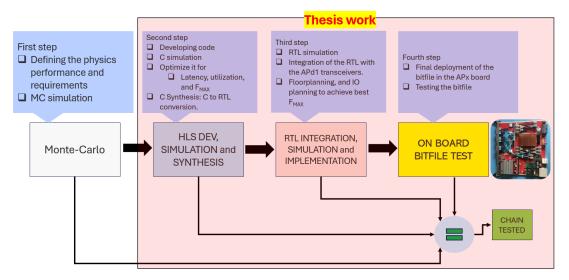

| 4.7 | Design flow of the Phase-2 calorimeter trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 48                              |

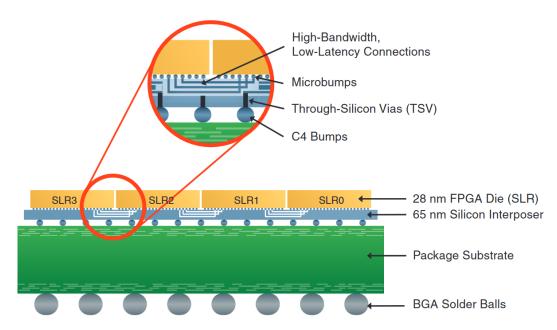

| 4.8 | FPGA fabricated using SSI technology [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 49                              |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                 |

List of Figures xiii

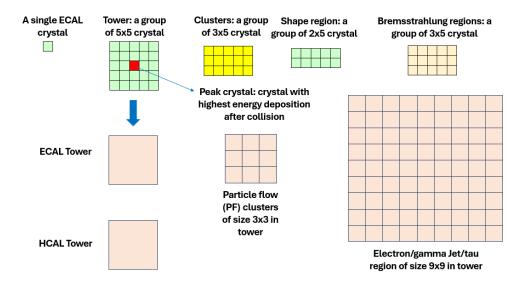

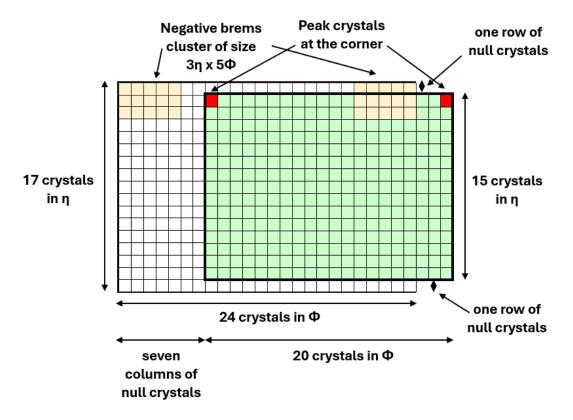

| 5.1  | Illustration of the ECAL crystal, tower, HCAL tower, and the electron/photon clusters. The clustering includes the bremsstrahlung losses in the $phi$                                                                                                                                                                                                                                       |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | direction and jets region to account for the hadronization of quarks and gluons. The particle flow (PF) clustering is considered for the correlator                                                                                                                                                                                                                                         |    |

|      | trigger                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

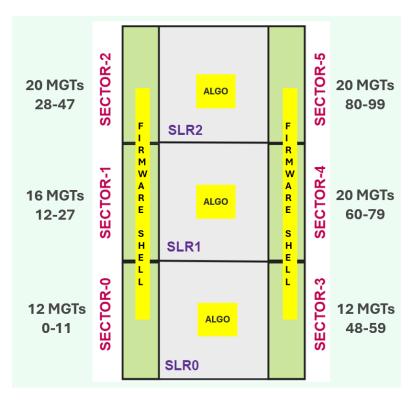

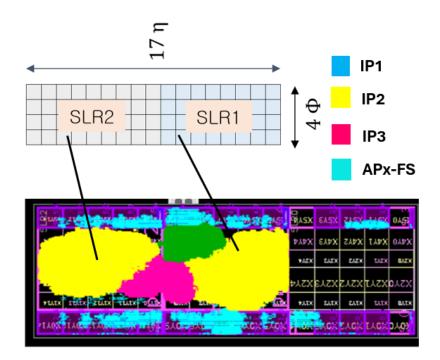

| 5.2  | Floorplan of the XCVU9P FPGA. The device is fabricated by stacking three SLR dies. The MGTs of the FPGA are instantiated using the APx firmware shell, which is implemented in six sectors. The firmware shell is located at the boundary, near the MGTs location [6]                                                                                                                       | 54 |

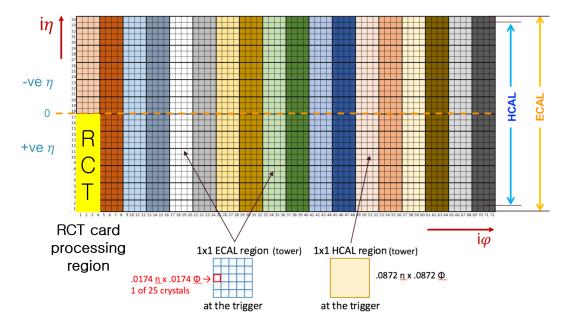

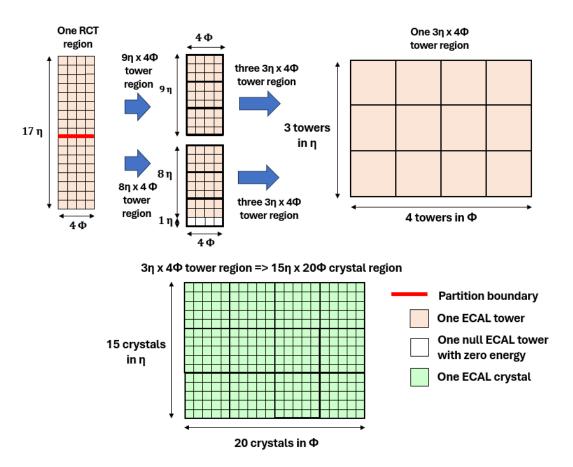

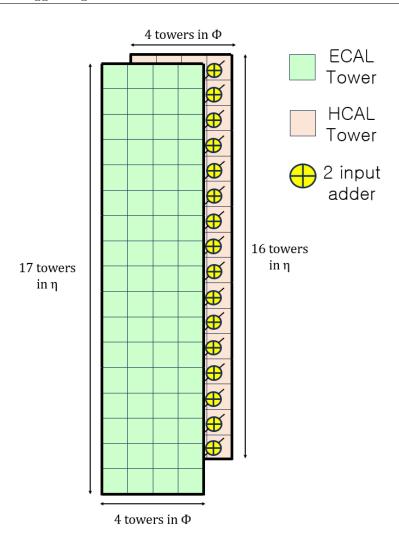

| 5.3  | CMS barrel calorimeter geometry, including the ECAL and HCAL detectors. The processing region of one RCT board, i.e., $17\eta \times 4\phi$ towers in                                                                                                                                                                                                                                       |    |

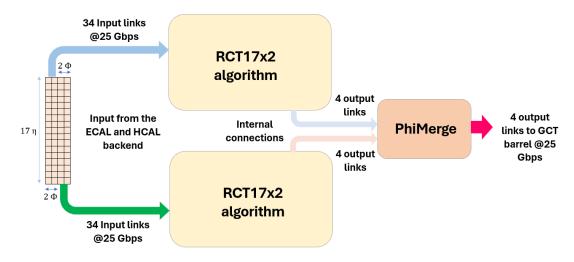

| 5.4  | ECAL and $16\eta \times 4\phi$ towers in HCAL, is highlighted in the yellow box [40]. Two-stage architecture of the RCT v1.0 algorithm. The first level employs two identical RCT17x2 algorithms processing the crystal information. The second stage is implemented using the PhiMerge algorithm, which combines the information from the first level and sends it to the GCT barrel board | 56 |

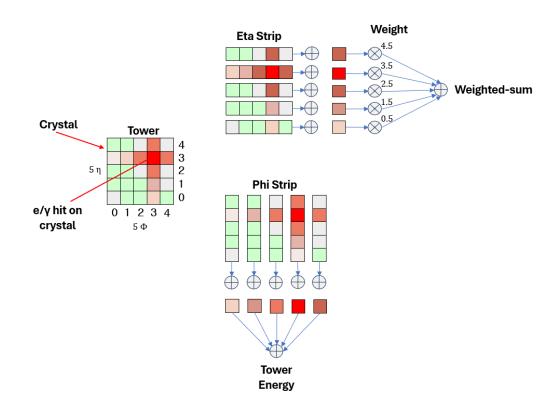

| 5.5  | The illustration of energy-weighted sum algorithm for finding peak in a tower                                                                                                                                                                                                                                                                                                               | 59 |

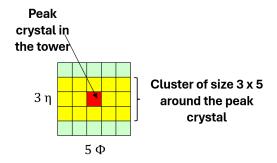

| 5.6  | Cluster formation of size $3\eta \times 5\phi$ around the peak crystal energy in an ECAL tower                                                                                                                                                                                                                                                                                              | 59 |

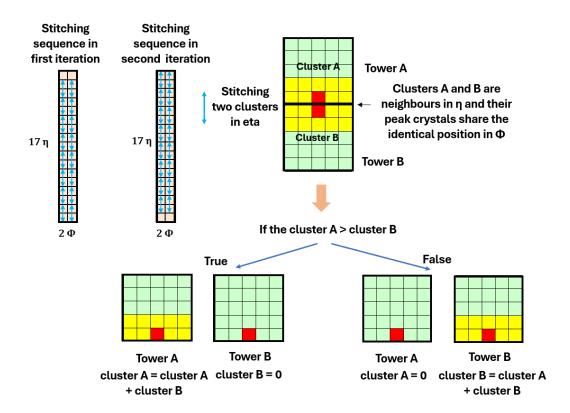

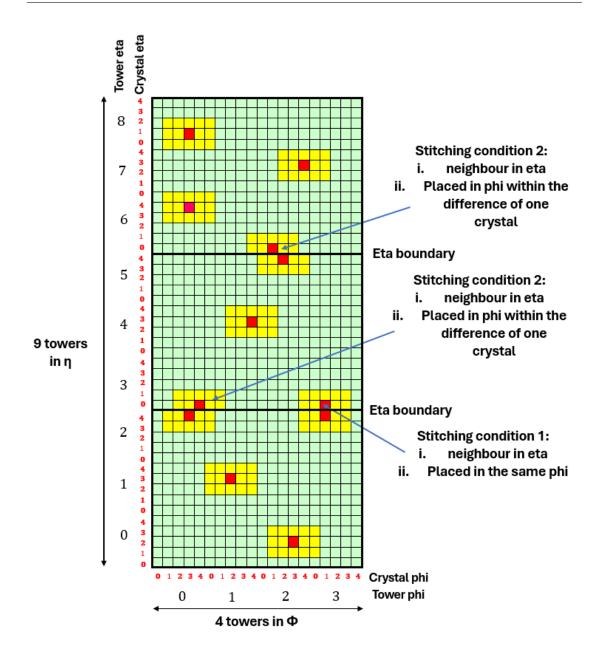

| 5.7  | Stitching logic of clusters in eta. The double-sided arrow in the $17\eta \times 2\phi$ RCT geometry signifies the direction of stitching in $eta$ direction                                                                                                                                                                                                                                | 60 |

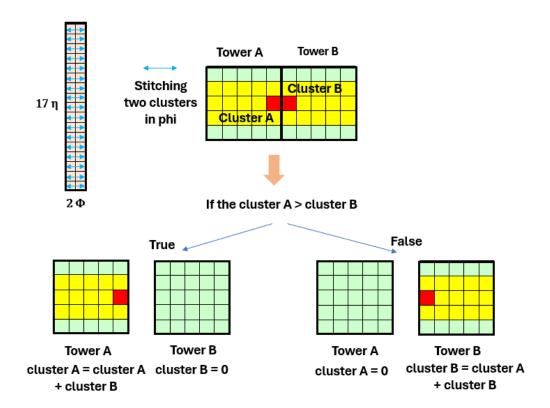

| 5.8  | Stitching logic of clusters in $phi$ . The double-sided arrow in the $17\eta \times 2\phi$ RCT geometry signifies the direction of stitching in $phi$ direction                                                                                                                                                                                                                             | 61 |

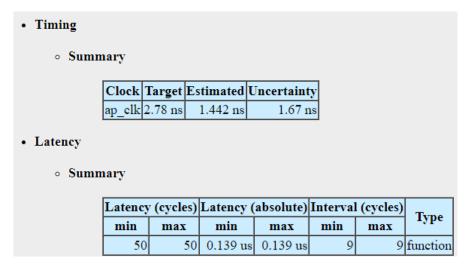

| 5.9  | RCT17x2 HLS latency report                                                                                                                                                                                                                                                                                                                                                                  | 61 |

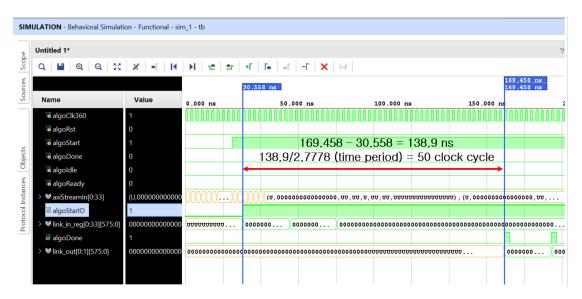

| 5.10 | RCT17x2 RTL simulation validating the latency of 50 clock cycle                                                                                                                                                                                                                                                                                                                             | 62 |

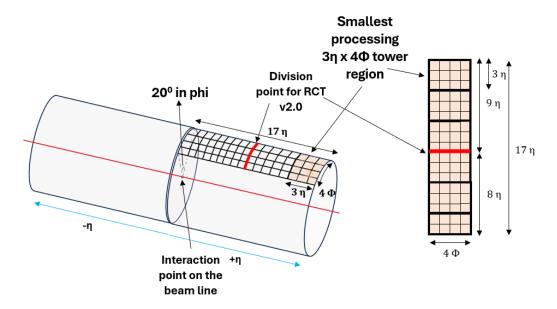

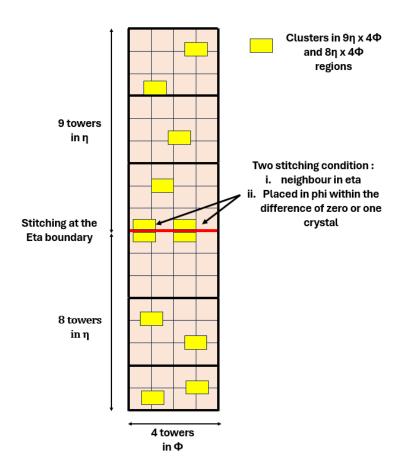

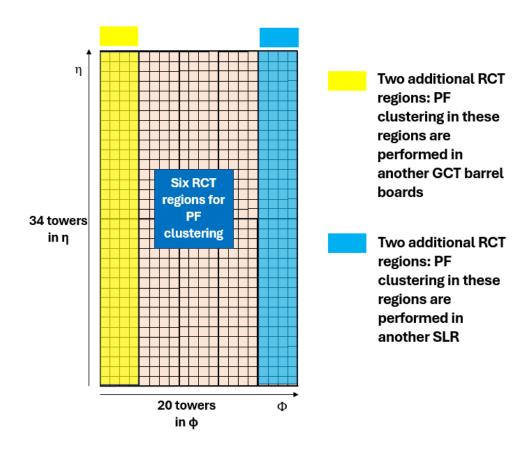

|      | RCT v2.0 covering region in the CMS ECAL barrel                                                                                                                                                                                                                                                                                                                                             | 63 |

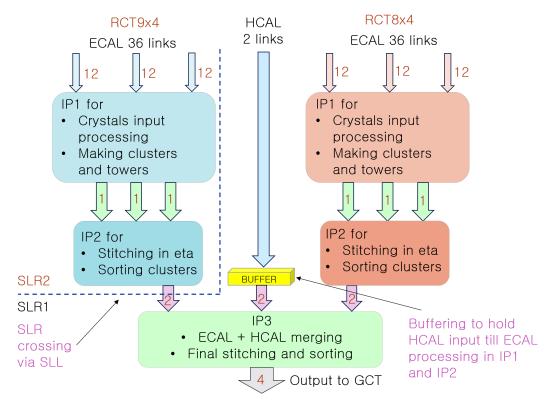

|      | RCT v2.0 architecture with a regional partition in two tower region of $9\eta \times 4\phi$ and $8\eta \times 4\phi$ , and functional division into three IPs or algorithms labeled IP1, IP2, and IP3                                                                                                                                                                                       | 64 |

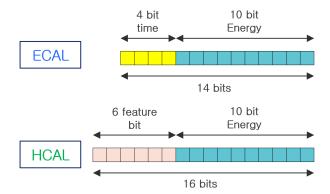

| 5 13 | RCT v2.0 ECAL crystal and HCAL tower input bits pattern                                                                                                                                                                                                                                                                                                                                     | 66 |

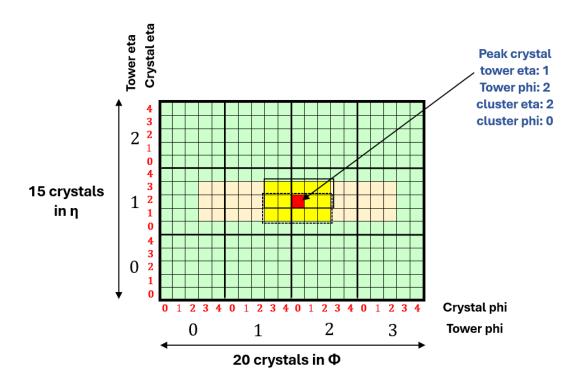

|      | IP1 ECAL crystal mapping in $15\eta \times 20\phi$ crystal region                                                                                                                                                                                                                                                                                                                           | 67 |

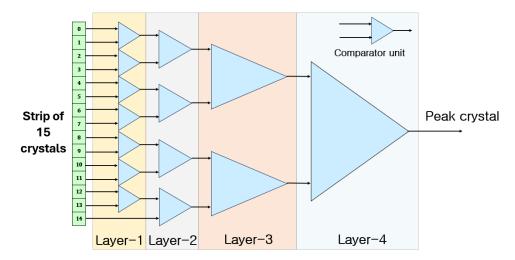

|      | IP1 peak finding using multi-level comparison strategy                                                                                                                                                                                                                                                                                                                                      | 68 |

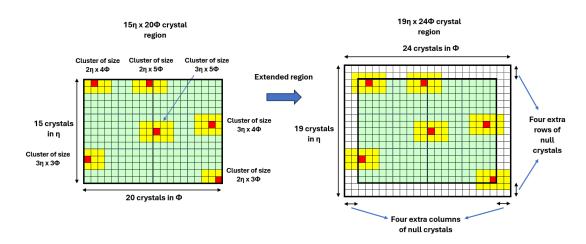

|      | Various clustering regions in IP1 based on the peak crystal position (left) in the $15\eta \times 20\phi$ crystal geometry. The extension of the crystal geometry from $15\eta \times 20\phi$ to $19\eta \times 24\phi$ by adding null crystals in <i>eta</i> and <i>phi</i> reduces all the cluster dimensions to a single $3\eta \times 5\phi$ crystal region (right)                     | 69 |

| E 17 |                                                                                                                                                                                                                                                                                                                                                                                             | 09 |

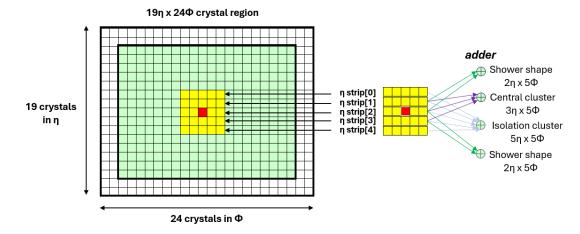

|      | Computation of the central, shape, and isolation cluster in IP1 in the $19\eta \times 24\phi$ crystal geometry                                                                                                                                                                                                                                                                              | 69 |

| 5.18 | IP1 negative brem cluster computation with respect to the central cluster. The figure highlights the mapping of the main crystal region of $15\eta \times 20\phi$ to the extruded region of $17\eta \times 24\phi$ . The corner cases of making brem                                                                                                                                        |    |

| 5.19 | clusters are shown with the two peak crystals positioned at the two corners. IP1 clustering scheme depicting the central (yellow), shape (covered in dashed and solid black lines around the peak crystal), and brems clusters.                                                                                                                                                             | 70 |

|      | The peak crystal (red) position is encoded in terms of tower <i>eta</i> , tower <i>phi</i> , crystal <i>eta</i> , and crystal <i>phi</i>                                                                                                                                                                                                                                                    | 71 |

List of Figures xiv

| 5.20 | IP1 tower energy calculation. The figure highlights the twelve towers                           |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | in the region of $15\eta \times 20\phi$ crystals and demonstrates the tower energy              |    |

|      |                                                                                                 | 72 |

|      |                                                                                                 | 73 |

|      |                                                                                                 | 75 |

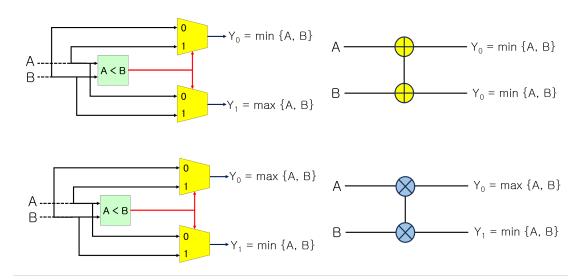

| 5.23 | CAE block high-level implementation with the increasing (up) and de-                            |    |

|      | creasing (down) order depicted with the corresponding symbols and equa-                         |    |

|      | tion                                                                                            | 76 |

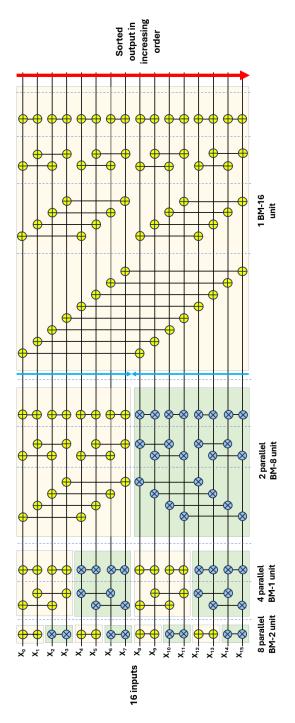

| 5.24 | 16-input bitonic sort grid comprising 10 levels of CAE block. It sorts the                      |    |

|      | input in increasing order                                                                       | 77 |

| 5.25 | 16-input bitonic sort HLS synthesis report                                                      | 78 |

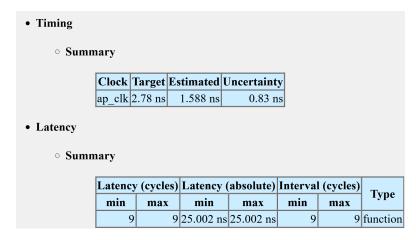

| 5.26 | RCT region of $9\eta \times 4\phi$ highlighting the six highest clusters (after bitonic         |    |

|      | sort) candidates for the IP3 and the adding back of one of the un-selected                      |    |

|      | clusters with the tower. The highlighted un-selected cluster's peak crystal                     |    |

|      | is inside tower number 5 of the region. Therefore, the cluster energy will                      |    |

|      | · 5                                                                                             | 78 |

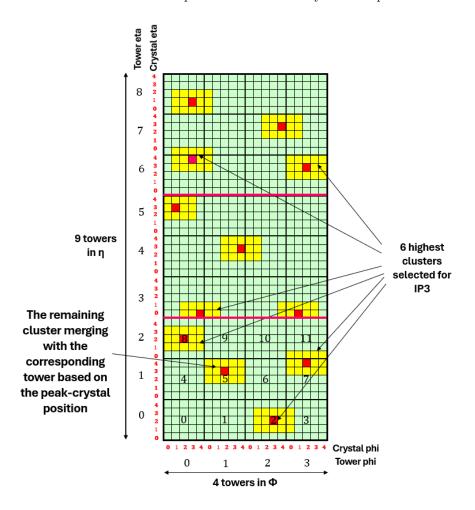

| 5.27 | The IP2 HLS timing reports                                                                      | 79 |

|      | ·                                                                                               | 80 |

| 5.29 | ECAL and HCAL towers addition                                                                   | 81 |

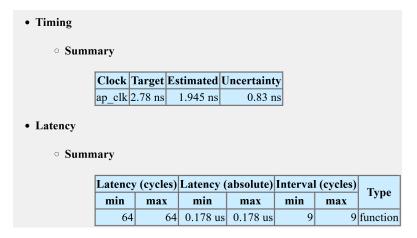

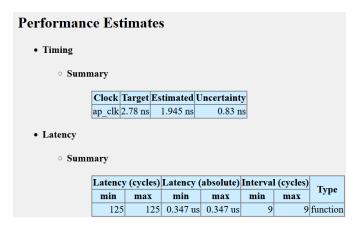

| 5.30 | IP3 HLS timing report highlighting the latency of 125 clock cycle                               | 81 |

| 5.31 | Two layer organization of GCT comprising GCT barrel, endcap and sum                             |    |

|      | algorithm                                                                                       | 84 |

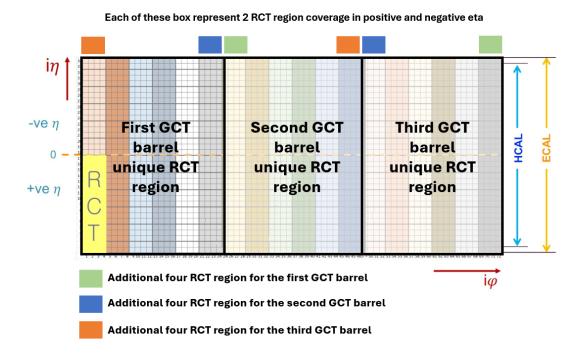

| 5.32 | Calorimeter barrel region segmentation in three GCT barrel board. Each                          |    |

|      | board comprises 12 unique RCT regions and 4 additional RCT regions                              |    |

|      | from either side of $phi$                                                                       | 85 |

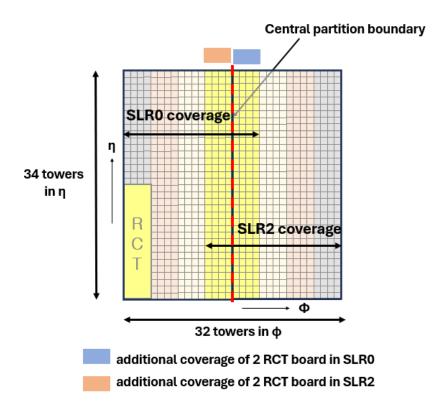

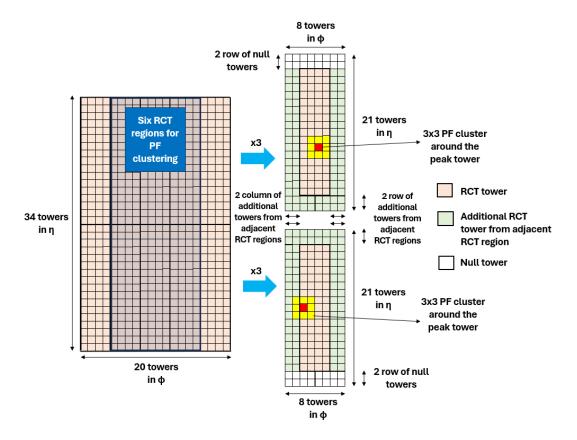

| 5.33 | Partition of one GCT barrel region in two SLR. Each SLR takes input                             |    |

|      | from ten RCT regions                                                                            | 86 |

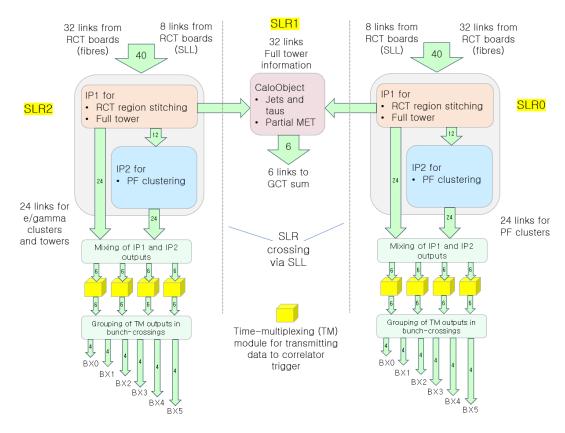

| 5.34 | GCT barrel architecture                                                                         | 87 |

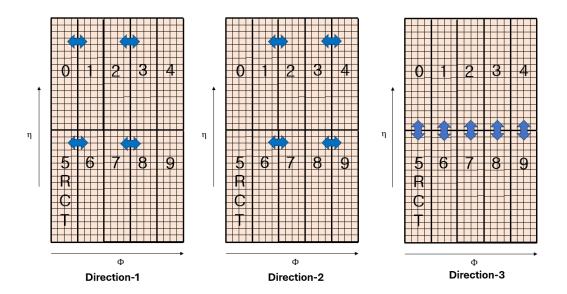

| 5.35 | Stitching of the RCT regions in three directions. Direction-1 and Direction-                    |    |

|      | 2 represent the stitching at the phi boundaries and Direction-3 at the eta                      |    |

|      |                                                                                                 | 88 |

| 5.36 | GCT barrel region highlighting the PF clustering coverage of the RCT                            |    |

|      |                                                                                                 | 90 |

| 5.37 | Full tower geometry of ten RCT regions. The six unique RCT regions are                          |    |

|      | emphasized inside the grey box. One RCT region with additional adjacent                         |    |

|      | towers is highlighted, along with one PF cluster and the corresponding                          |    |

|      |                                                                                                 | 91 |

|      |                                                                                                 | 92 |

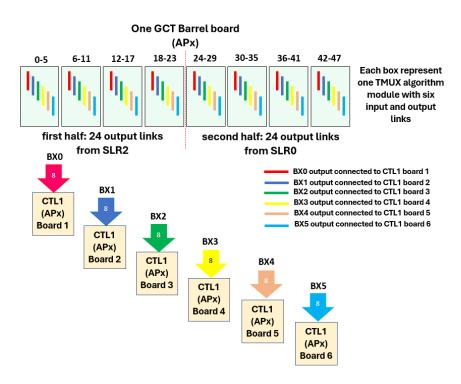

|      | Connection of one GCT barrel board with six correlator layer-1 APx boards.                      | 93 |

| 5.40 | Input processing region of CaloObject algorithm highlighting the spread                         |    |

|      | of one jet/taus in $9\eta \times 9\phi$ tower region                                            | 94 |

| 5.41 | The conversion of tower geometry of size $32\eta \times 34\phi$ into two $24\eta \times 36\phi$ |    |

|      | tower regions. A supertower is highlighted in the red square box depicting                      |    |

|      |                                                                                                 | 95 |

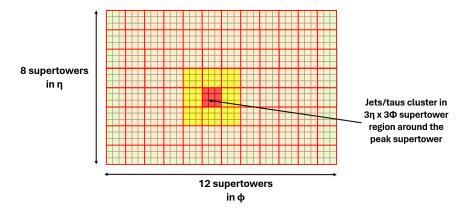

|      | Jet/taus cluster and peak supertower in the $12\eta \times 8\phi$ supertower region             | 95 |

|      |                                                                                                 | 96 |

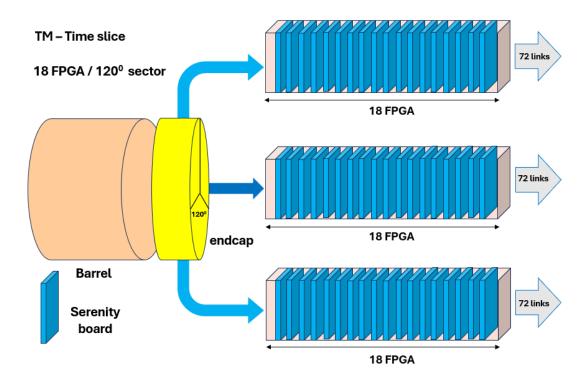

| 5.44 | HGCAL backend (one endcap) connection with three GCT endcap boards.                             | 98 |

List of Figures xv

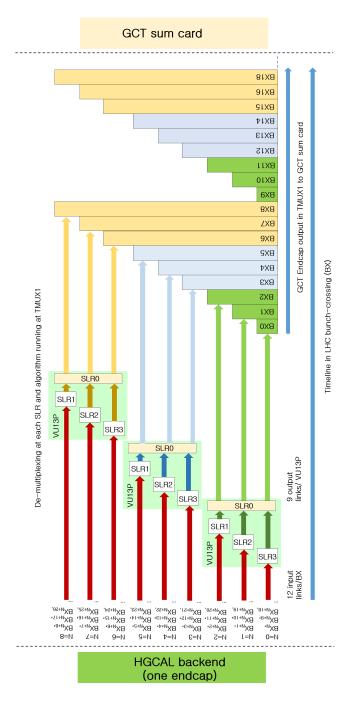

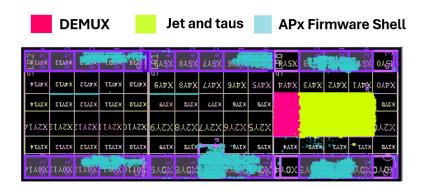

| 5.45       | GCT endcap architecture. The demultiplexing of the entire endcap is performed using three XCVU13P FPGAs. Out of four SLRs, each SLR1-3 receives two bunch-crossing information, which are nine clock cycles apart. The algorithm performs the demultiplexing and provides input in the TMUX1 interval to the jet algorithm. The output from three SLRs                                                                                 |       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

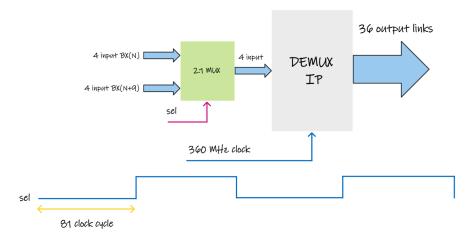

| 5.46       | is merged in the SLR0 and sent to the GCT sum board at TM1 interval. The demultiplexing scheme of the DEMUX algorithm using a two-input                                                                                                                                                                                                                                                                                                |       |

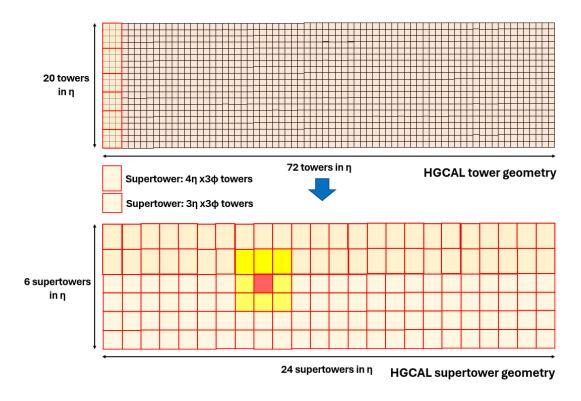

| 5.47       | multiplexor. The two inputs have a time difference of 9 bunch-crossings. HGCAL tower geometry and the supertower geometry. It also highlights one peak supertower and the jet/taus of size $3\eta \times 3\phi$ in supertower                                                                                                                                                                                                          |       |

| 5.48       | GCT endcap jets and taus algorithm latency report                                                                                                                                                                                                                                                                                                                                                                                      |       |

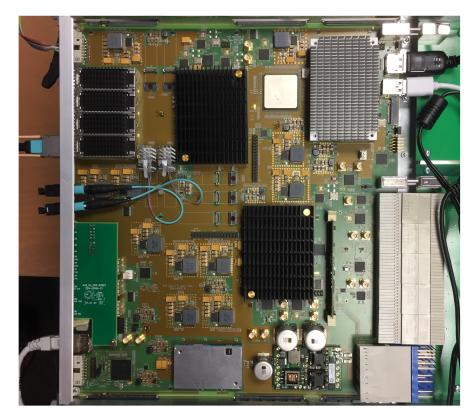

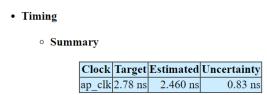

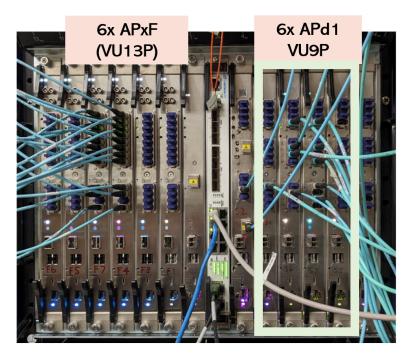

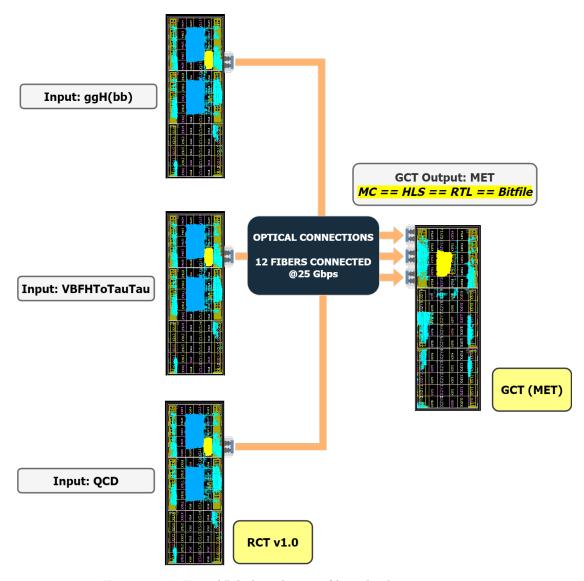

| 6.1        | ATCA crate at the University of Wisconsin lab hosting six APd1 board (XCVU9P) and six APxF board (XCVU13P). Four APd1 boards are used to prototype the Phase-2 Level-1 calorimeter trigger                                                                                                                                                                                                                                             | 107   |

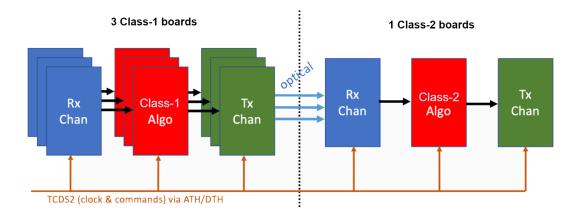

| 6.2        | Multi-boards test setup.                                                                                                                                                                                                                                                                                                                                                                                                               |       |

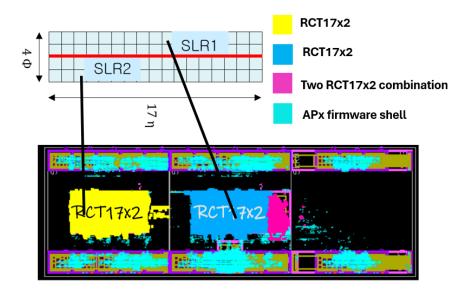

| 6.3        | RCT v1.0 firmware implementation. The two 17x2 regions are implemented in SLR2 and SLR1 (8 clock regions each), respectively. Both the                                                                                                                                                                                                                                                                                                 | . 100 |

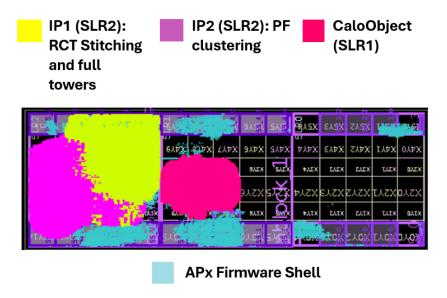

| 6.4        | regions are combined in the SLR1 (two clock regions) RCT v2.0 firmware implementation. The two IP1 and two IP2 of $8\eta \times 4\phi$                                                                                                                                                                                                                                                                                                 | . 109 |

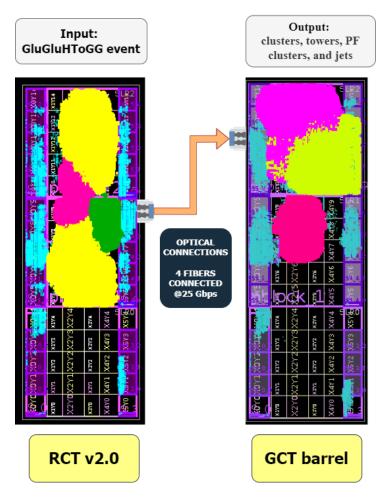

|            | and $9\eta \times 4\phi$ tower regions are implemented in SLR1 and SLR2, respectively. The IP3 is implemented in SLR1                                                                                                                                                                                                                                                                                                                  | . 111 |

| 6.5        | GCT barrel firmware implementation on XCVU9P FPGA. The IP1 and IP2 is implemented in SLR2 and CaloObject algorithm is implemented in                                                                                                                                                                                                                                                                                                   |       |

|            | SLR1                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 112 |

| 6.6        | GCT barrel firmware implementation on XCVU9P FPGA. The IP1 and IP2 is implemented in SLR2 and CaloObject algorithm is implemented in                                                                                                                                                                                                                                                                                                   | 110   |

| 6 7        | SLR1                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 6.7<br>6.8 | GCT sum v1.0 algorithm placed in SLR2 (highlighted in green) GCT sum v2.0 algorithm placed in SLR0 (highlighted in green)                                                                                                                                                                                                                                                                                                              |       |

| 6.9        | Four APd1 boards test of barrel calorimeter trigger                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 6.10       | Two APd1 boards test of barrel calorimeter trigger                                                                                                                                                                                                                                                                                                                                                                                     |       |

|            | Connection of the four APd1 boards used for prototyping the entire Phase-2 Level-1 calorimeter trigger. It highlights the firmware used at the RCT, GCT barrel, GCT endcap, and GCT sum together with the                                                                                                                                                                                                                              |       |

|            | optical connection made                                                                                                                                                                                                                                                                                                                                                                                                                | . 119 |

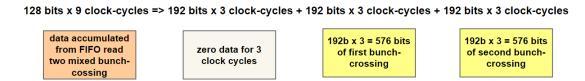

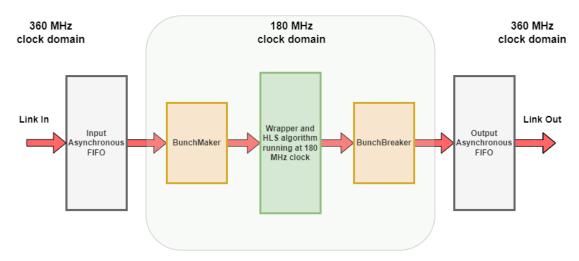

| A.1        | Write and read scheme of the asynchronous FIFO for two LHC bunch-crossing. Write operation in FIFO is performed using 64 bit of data word at the write clock of 360 MHz. It takes 9 clock cycles to complete the write operation of one bunch-crossing. The read operation of FIFO is performed using 128 bits of data word at the read clock of 180 MHz. The mixing of two bunch consecutive bunch-crossing will occur at every fifth |       |

|            | read operation                                                                                                                                                                                                                                                                                                                                                                                                                         |       |