# Digitally Intensive Sub-Sampling Mixer-First RF Front-End Architectures in 1.2 V, 65 nm CMOS

A thesis submitted for the degree of

**Doctor of Philosophy**

In

**Electronics Science and Engineering**

By

# Rakesh Varma Rena (17PHPE03)

Center for Advanced Studies in Electronics Science and Technology

University of Hyderabad

Telangana-500046, India

June-2023

#### **DECLARATION**

I hereby declare that the matter embodied in this thesis titled "Digitally Intensive Sub-Sampling Mixer-First RF Front-End Architectures in 1.2 V, 65 nm CMOS" submitted to the University of Hyderabad for the award of Doctor of Philosophy in Electronics Science and Engineering is a record of original research work carried out by me under the supervision of Dr. Vijay Shankar Pasupureddi and Prof. M. Ghanashyam Krishna, Center for Advanced Studies in Electronics Science and Technology (CASEST), School of Physics, University of Hyderabad. To the best of my knowledge, the thesis is not submitted for any degree in any University or institute.

Date: 26-06-2023

Place: Hyderabad Mr. Rakesh Varma Rena

Rakesh Rena

#### CERTIFICATE

(For Ph.D. Dissertation)

This is to certify that the thesis entitled "Digitally Intensive Sub-Sampling Mixer-First RF Front-End Architectures in 1.2 V, 65 nm CMOS" submitted by Mr. Rakesh Varma Rena bearing registration number 17PHPE03 in partial fulfilment of the requirements for the award of Doctor of Philosophy in Center for Advanced Studies in Electronics Science and Technology (CASEST), School of Physics is a bonafide work carried out by her under my supervision and guidance.

This thesis is free from plagiarism and has not been submitted previously in part or in full to this or any other University or Institution for the award of any degree or diploma.

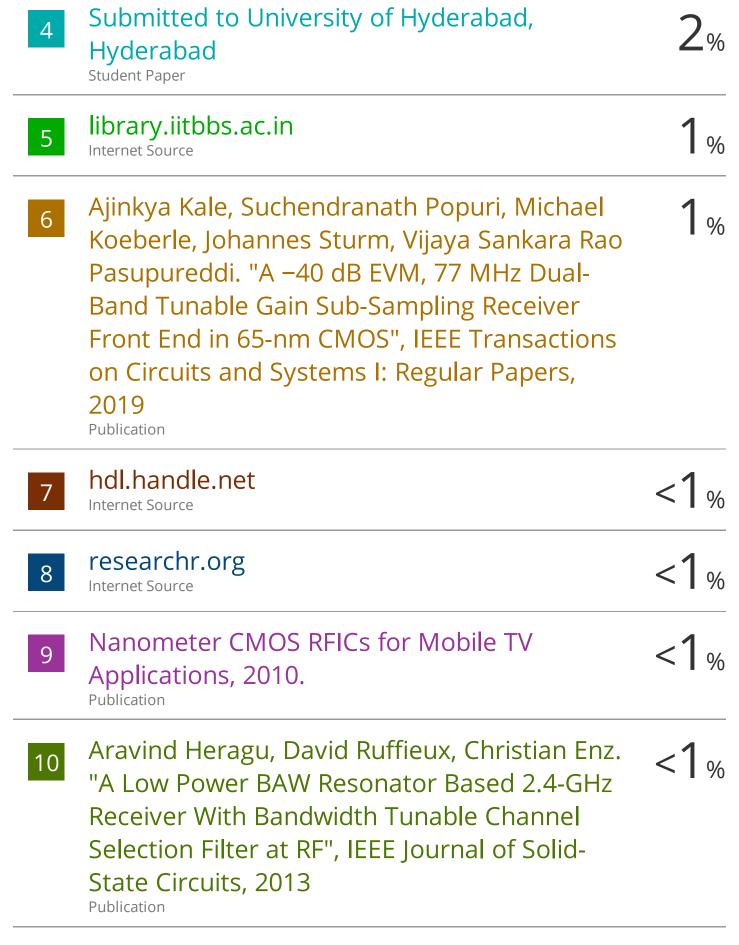

Further, the undertaken work has the following publications before submission of the thesis for adjudication and has produced evidence for the same in the form of an acceptance letter or the reprint in the relevant area of his research:

#### Journal publications:

- Rakesh Varma Rena, Raviteja Kammari, Vijay Shankar P., "0.4-1GHz Subsampling Mixer-First RF Front-End with 50dB HR3, +10dBm IB-IIP3 in 65nm CMOS", in IEEE Transactions On Very Large Scale Integration (VLSI) Systems, DOI: 10.1109/TVLSI.2023.3269011.

- 2. Rakesh Varma Rena, Raviteja Kammari, and Vijay Shankar Pasupureddi "0.4-1.8

GHz, 90 MHz BW, 4.7 dB NF quarter-rate sub-sampling mixer-first direct downconversion RF front-end", is submitted to IEEE Transactions On Very Large Scale Integration (VLSI) Systems(under review).

#### Conference proceedings:

- 1. Rakesh Rena, Suraj Kumar Verma and Vijaya Sankara Rao Pasupureddi, "A Process Scalable Architecture for Low Noise Figure Sub-Sampling Mixer-First RF Front-End," 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021, pp. 1-5, doi: 10.1109/ISCAS51556.2021.9401387.

- 2. Rakesh Rena, Raviteja Kammari and Vijaya Sankara Rao Pasupureddi, "Digitally Intensive Sub-sampling Mixer-First Direct Down-Conversion Receiver Architecture," 2022 IEEE 65th International Midwest Symposium on Circuits and Systems (MWSCAS), Fukuoka, Japan, 2022, pp. 1-4, doi: 10.1109/MWSCAS54063.

Further, the student has passed the following courses towards fulfillment of coursework requirement for Ph.D.

| S.No. | Course Code | Name                                              | Credits | Pass/Fail |

|-------|-------------|---------------------------------------------------|---------|-----------|

| 1     | PE 803      | Analog and Mixed Signal Integrated Circuit Design | 4       | Pass      |

| 2     | PE 851      | Digital Integrated Circuit Design                 | 4       | Pass      |

| 3     | PE 802      | Research Methodology                              | 4       | Pass      |

Dr. Vijay Shankar Pasupureddi

Mayshankaij

Supervisor

Prof. M. Ghanashyam Krishna

M. Thanashyam

Co-Supervisor

M. Manashyam

Head, CASESTASEST

(Centre for Advanced Studies in Electronics Science & Technolo School of Physics University of Hyderabad-50

Dean, School of Physics

संकाय अध्यक्ष / Dean भौतिकी संकाय / School of Physics हैदराबाद विश्वविद्यालय

UNIVERSITY OF HYDERABAD हैदराबाद / HYDERABAD-500 046. भारत / INDIA.

## Dedicated

To my parents

Lalitha Rena and Narsaiah Rena

### Acknowledgements

I wish to express my sincere thanks to all people in my life who contributed directly and indirectly to the successful completion of my Ph.D. work.

First and foremost, I would like to express my sincere gratitude to my research supervisor **Dr. Vijay Shankar Pasupureddi**, for guiding me over the past six years for his continuous support from starting day of research to till the completion of this thesis. Without his continuous support and motivation, it would not have been possible for me to design and measure an RF test-chip.

I am grateful to my co-supervisor and doctoral committee members **Prof.** M. Ghanashyam Krishna and **Prof.** S.L. Sabat for their encouragement and for giving suggestions in the discussions throughout my Ph.D.

I am thankful to all the faculty of CASEST, Prof. Rajaram Guruswamy, Prof. K.C. James Raju, Prof. S.V.S. Nageswar Rao, Dr. Bhawna Gomber, Dr. Anjali Priya, and Dr. Pratap Kollu, for their support.

I thank present and former Heads, CASEST and Deans, the School of Physics, for the support and facilities provided. Their timely support and kind response lead to the smooth progress of my research work.

I would like to thank non-teaching staff and technicians, Mr. Ravibabu and Mr. Sudarshan for their help and support in the administrative work.

I would like to thank my research colleagues Mounika, Suraj, and Raviteja for being there day in and day out during the second and third years of my course. Especially, my dear friend, Raviteja is there from finalizing ideas to testing the chip performance. I would like to express my sincere thanks to Dr. Ajinkya Kale for spending his valuable time discussing switch-capacitor simulations during the first year of my course.

I would like to express my sincere thanks to my colleagues Prema Kumar, Sandeep, Eshwar, Pankaj, Jagapathi, Srikanth, Babu Rao, Srinivas and other friends at CASEST Venkat, Bhavana, Sai Prasad, Piyush, Yogi, Shiva, Sampath, Vivek, Saidulu and Rajesh for their support during various discussions. Especially, Babu Rao helped while designing and finalizing the layout.

I want to thank Sravan, Chaitanya, Ashwini and Sai, who helped to set up the tool in our lab and Jatin and Siva Rama Krishna for guiding me while designing the test PCB.

I want to thank Gnanashekar, Chaitanya and Guru and other friends for the supporting me during the chip measurement.

I want to thank my friends Prasad, Anil, Vinay, Arun, Raja Shekhar and Venkatesh for always being there to support me, no matter what.

Finally, I would like to thank my uncles Mr. Ashok Koduri, Mr. Narsaiah Allam for their constant guidance and support throughout my education. I also want to thank my sister Ravali, brother Venkatesh and brother-in-law Sai Ram Charan for the supporting me over the years.

I acknowledge financial support from UGC-NET JRF fellowship, Meity-Government of India, IIT Bhubaneswar, for chip, PCB fabrication and Head CASEST for providing components for PCB.

#### Abstract

To meet the ever-growing need for connected devices, advanced wireless systems have to accommodate tens of billions of wireless devices to support a wide range of applications in various communication standards. The wireless communication standards such as IEEE 802.15.4-2020 are designed to provide better coverage for low-cost, portable wireless systems with limited power consumption for various applications such as smart utility networks(SUN), rail communications and control(RCC), healthcare and industrial monitoring. These applications operate in multiple bands over a wide frequency range from 0.16 GHz to 2.4 GHz and have low data rates; hence, they should consume low power for long battery life. To meet these requirements, the receiver's RF front-end must be re-configurable, and power consumption needs to be low while maintaining the sensitivity of the receiver. The mixer-first RF front-end architecture operates over a wide range of frequencies by tuning its local oscillator frequency or sampling frequency( $f_s$ ). Therefore, a single mixer-first RF front-end is sufficient to cover complete or most of the sub-2.4 GHz IEEE 802.15.4e standard applications.

The mixer-first receivers employ N-path mixers and filters, which are excited by non-overlapping clock phases and hence require clock dividers to generate precise multi-phase non-overlapping clocks. These dividers require a reference clock frequency of  $Nf_s/2$  for generating non-overlapping clocks with a frequency,  $f_s$ . In RF sampling-based mixer-first RF front-ends requires a sampling frequency greater than or equal to  $f_s$ , which increases the power consumption of these non-overlapping clock generation and distribution circuitry increases with the increasing  $f_s$ . In addition, the stringent jitter requirements increase the power consumption of the frequency synthesizers at high frequencies. Hence, the power consumption of the clock generation circuit is no longer negligible since it increases with the input RF frequency,  $f_{RF}$ . On the other hand, the sub-sampling down-conversion requires a low clock frequency and hence reduces the power consumption of non-overlapping clock generation, distribution circuits, and frequency synthesizer. However, the sub-sampling down-conversion has not been employed in mixer-first receiver RF front-ends due to the disadvantage of high noise figure from inherent noise folding and lack of RF port impedance matching because of non-zero IF down-conversion. Therefore, the main focus of this thesis

is to design digitally intensive sub-sampling mixer-first RF front-ends.

To address these issues, the first half of the thesis focuses on developing a sub-sampling multi-path down-conversion mixer scheme to reject the harmonic down-conversion to odd multiples of  $f_s/4$ , thereby alleviating the effect of noise folding and leading to a low noise figure. In addition, an IF stage impedance matching scheme is proposed that provides a 50  $\Omega$  impedance at the RF port of the mixer using an IF stage M-phase switch-capacitor band-pass filter connected in shunt at the input of the IF-LNA. Therefore, by employing these two schemes, a first of its kind process scalable low noise figure highly linear sub-sampling mixer-first RF front-end is proposed in this work. However, this work is also a non-zero IF down-conversion which is heterodyne in nature, and hence the passive mixer transparency property can not be exploited without the need for an additional circuit at the IF, such as M-phase filter for providing impedance matching at the RF port by impedance translation. To address this issue, a unique feature of sub-sampling, i.e. quarter-rate sub-sampling, is exploited, and a direct down-conversion scheme is proposed in this work.

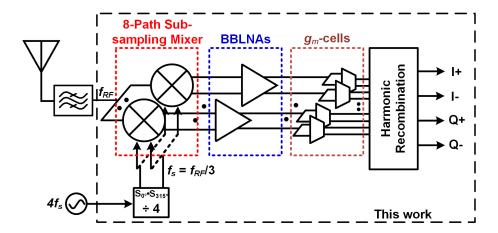

The second part of the thesis presents the above mentioned concept of a quarterrate sub-sampling direct down-conversion scheme using a sampling frequency at least three times lower than the input RF frequency and a harmonic re-combination scheme for achieving direct down-conversion using the third harmonic of  $f_s$ . The proposed RF frontend simultaneously achieves quadrature direct down-conversion and impedance matching by using the third harmonic of the quarter-rate sub-sampling frequency,  $f_s$ . This way, the quarter-rate sub-sampling direct down-conversion scheme saves the power consumption of non-overlapping clock generation, distribution circuits, and frequency synthesizer than the traditional RF sampling down-conversion receivers. Therefore, by employing these schemes, a first of its kind quarter-rate sub-sampling mixer-first direct down-conversion RF front-end is proposed.

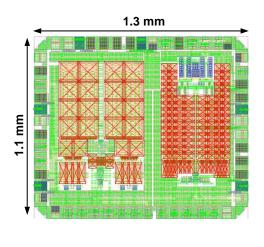

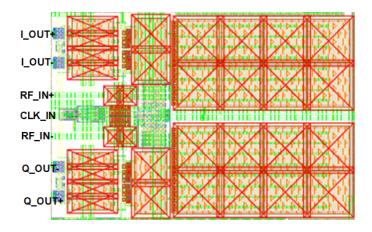

Finally, the proposed RF front-ends are implemented in 1.2 V, 65 nm CMOS technology and a test chip is fabricated to verify the performance predicted by analytical equations and circuit-level SpectreRF simulations. Both the proposed sub-sampling RF front-end prototypes are implemented on the same test chip, and the test chip occupies an active area of 0.65 mm<sup>2</sup>. The bare dies are directly attached to FR4 PCB and wire bonded to measure the performance of the test chip. The performance of both the RF front-ends is measured individually using various test setups. Verifying the results on four different

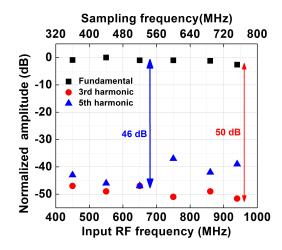

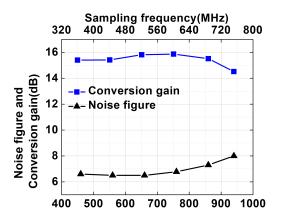

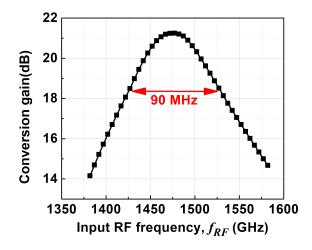

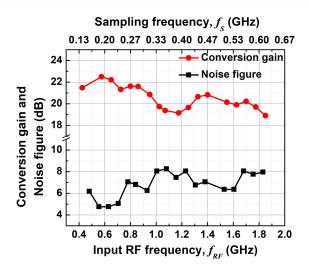

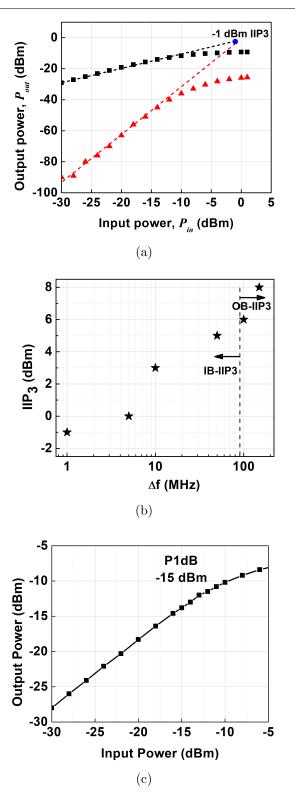

chips shows that the first RF front-end offers a wide-band operation from 0.4 - 1 GHz by tuning sampling frequency from 0.32 - 0.8 GHz with a minimum noise figure of 6.5 dB, 15.1 dB conversion gain and 50 dB third harmonic rejection. The proposed RF front-end exhibit IB-IIP<sub>3</sub> of +10 dBm OB-IIP<sub>3</sub> and +20 dBm. The second RF front-end offers wide-band operation over the frequency band 0.4 - 1.8 GHz by tuning a sampling frequency from 0.13 - 0.6 GHz with a bandwidth of 90 MHz. The receiver has a DSB noise figure of 4.7 dB, a conversion gain of 22 dB, an IB-IIP<sub>3</sub> of -1 dBm and OB-IIP<sub>3</sub> of +8 dBm. The switch-capacitor blocks in the first architecture consume 400  $\mu$ W, and the second architecture consumes a power of 800  $\mu$ W, which makes both the proposed switch-capacitor-based sub-sampling mixer-first RF front-ends suitable for low-power applications.

## Contents

| 1 | Intr | oaucti | ion        |                                                                                   | 1  |

|---|------|--------|------------|-----------------------------------------------------------------------------------|----|

|   | 1.1  | Trends | s in Wirel | less Communications                                                               | 1  |

|   | 1.2  | Digita | lly Intens | ive Switch-Capacitor RF Front-Ends                                                | 2  |

|   |      | 1.2.1  | RF Sam     | pling Based Switch-Capacitor RF Front-Ends                                        | 4  |

|   |      | 1.2.2  | Sub-Sam    | npling Based Switch-Capacitor RF Front-Ends                                       | 4  |

|   | 1.3  | Proble | em Definit | tion                                                                              | 5  |

|   | 1.4  | Litera | ture Surv  | ey                                                                                | 5  |

|   |      | 1.4.1  | Switch-C   | Capacitor Sub-Sampling RF Front-Ends                                              | 6  |

|   |      |        | 1.4.1.1    | Heterodyne Sub-Sampling Receiver in 0.18- $\mu m$ CMOS                            | 6  |

|   |      |        | 1.4.1.2    | A Low Noise Quadrature Sub-Sampling Mixer                                         | 7  |

|   |      |        | 1.4.1.3    | A Sub-Sampling Dual-Band Tunable Gain Receiver in 65-nm CMOS                      | 9  |

|   |      | 1.4.2  | Switch-C   | Capacitor RF Sampling Based RF Front-Ends                                         | 9  |

|   |      |        | 1.4.2.1    | A Switched-Capacitor RF Front-End With Embedded Programmable High-Order Filtering | 10 |

|   |      |        | 1.4.2.2    | A Passive Mixer-First Receiver With Widely Tunable RF Interface                   | 11 |

|   |      | 1.4.3  | Wide-ba    | and Receivers for Software-Defined Radio Applications                             | 12 |

|   | 1.5  | Resear | rch Gaps   | and Thesis Objectives                                                             | 13 |

|   |      | 1.5.1  | Research   | n Gaps                                                                            | 13 |

|   |     | 1.5.2  | Thesis Objectives                                                                           | 15 |

|---|-----|--------|---------------------------------------------------------------------------------------------|----|

|   | 1.6 | Propos | sed Solutions                                                                               | 15 |

|   |     | 1.6.1  | A Process Scalable Architecture for Low Noise Figure Sub-Sampling  Mixer-First RF Front-End | 16 |

|   |     | 1.6.2  | Digitally Intensive Sub-Sampling Mixer-First Direct Down-Conversion RF Front-End            | 17 |

|   | 1.7 | Thesis | Contribution                                                                                | 18 |

|   | 1.8 | Thesis | Organization                                                                                | 20 |

| 2 |     |        | Scalable Architecture for Low Noise Figure Sub-Sampling st RF Front-End                     | 23 |

|   | 2.1 | Sub-Sa | ampling Wireless Links for Low-Power Radios                                                 | 23 |

|   |     | 2.1.1  | Sub-Sampling Down-Conversion: A Low-Power Paradigm                                          | 23 |

|   |     | 2.1.2  | Sub-Sampling RF Front-End for Low-Power Application                                         | 25 |

|   | 2.2 |        | onic Rejection and Noise Figure of Sub-Sampling Mixer-First RF  End                         | 26 |

|   |     | 2.2.1  | Single Path Sub-Sampling Mixer                                                              | 26 |

|   |     | 2.2.2  | Harmonic Rejection Multi-Path Sub-Sampling Mixer                                            | 29 |

|   |     | 2.2.3  | Conversion Gain                                                                             | 31 |

|   |     | 2.2.4  | Noise Figure                                                                                | 33 |

|   |     | 2.2.5  | Linearity                                                                                   | 34 |

|   |     | 2.2.6  | Harmonic Rejection in the Presence of Mismatches                                            | 34 |

|   | 2.3 |        | eme for Sub-Sampling Mixer-First RF Front-End Input Impedance                               | 35 |

|   |     | 2.3.1    | Input Impedance of M-phase Switch-Capacitor Filter and IF-LNA .        | 36 |

|---|-----|----------|------------------------------------------------------------------------|----|

|   |     | 2.3.2    | Input Impedance of the Sub-Sampling RF Front-End                       | 38 |

|   |     | 2.3.3    | $Z_{in}(\omega_{IF})$ versus $C_H$                                     | 39 |

|   | 2.4 | System   | n Level Error Vector Magnitude(EVM) performance                        | 41 |

|   | 2.5 | Conclu   | asion                                                                  | 42 |

| 3 |     | itally l | Intensive Sub-Sampling Mixer-First Direct Down-Conversion  End         | 43 |

|   | 3.1 | Sub-sa   | ampling Direct Down-conversion Mixer-First RF Front-End Architec-      |    |

|   |     | ture     |                                                                        | 43 |

|   |     | 3.1.1    | Sub-Sampling Down-Conversion: A Low-Power Paradigm $\ \ldots \ \ldots$ | 43 |

|   | 3.2 | Quarte   | er-Rate Sub-Sampling Direct Down-Conversion Architecture               | 45 |

|   |     | 3.2.1    | Frequency Plan                                                         | 46 |

|   |     | 3.2.2    | Eight-Path Direct Down-Conversion Mixer and Harmonic Recombi-          |    |

|   |     |          | nation Scheme                                                          | 47 |

|   |     | 3.2.3    | Conversion Gain                                                        | 50 |

|   |     | 3.2.4    | Noise Figure                                                           | 51 |

|   |     | 3.2.5    | Linearity and Power Consumption                                        | 52 |

|   | 3.3 | Imped    | ance Matching Scheme                                                   | 54 |

|   | 3.4 | System   | n Level Error Vector Magnitude(EVM) Analysis                           | 57 |

|   | 3.5 | Conclu   | isions                                                                 | 58 |

| 4 | CM  | OS Im    | aplementation of Sub-Sampling RF Front-end Architectures               | 59 |

|   | 4.1 |          | cess Scalable Architecture for Low Noise Figure Sub-Sampling Mixer-    | 59 |

|     | 4.1.1 | Circuit  | Implementation                                          | 59 |

|-----|-------|----------|---------------------------------------------------------|----|

|     |       | 4.1.1.1  | Four-Path Sub-Sampling Mixer                            | 60 |

|     |       | 4.1.1.2  | IF-LNA                                                  | 60 |

|     |       | 4.1.1.3  | M-Phase Switch-Capacitor Filter                         | 61 |

|     |       | 4.1.1.4  | Measurement Buffer                                      | 62 |

|     |       | 4.1.1.5  | Non-Overlapping Clock Generator                         | 62 |

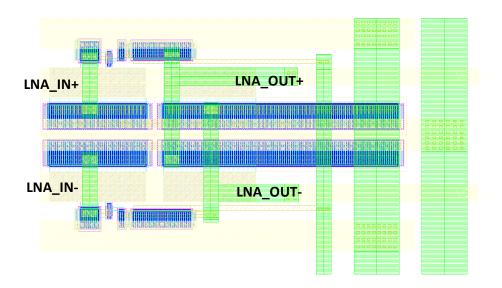

|     | 4.1.2 | Layout 1 | Implementation                                          | 63 |

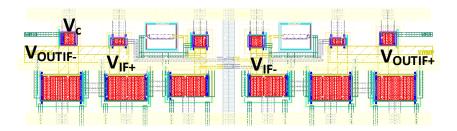

|     |       | 4.1.2.1  | Layout of the Switch-Capacitor Four-Path Mixer          | 63 |

|     |       | 4.1.2.2  | Layout of the IF-LNA                                    | 64 |

|     |       | 4.1.2.3  | Layout of the M-Path Filter                             | 64 |

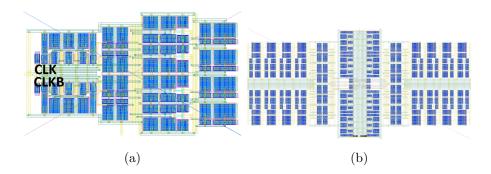

|     |       | 4.1.2.4  | Layout of the Non-Overlapping Clock Generation          | 64 |

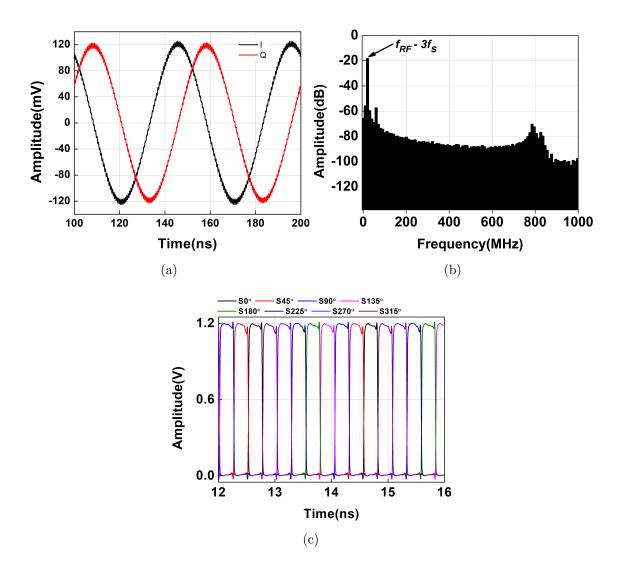

|     | 4.1.3 | Post-Lag | yout Performance                                        | 66 |

|     |       | 4.1.3.1  | Transient Simulation                                    | 66 |

| 1.2 |       | Ü        | sive Sub-Sampling Mixer-First Direct Down-Conversion RF | 67 |

|     |       |          |                                                         |    |

|     | 4.2.1 | Circuit  | Implementation                                          |    |

|     |       | 4.2.1.1  | Eight-Path Switch-Capacitor Mixer                       | 68 |

|     |       | 4.2.1.2  | BBLNA                                                   | 69 |

|     |       | 4.2.1.3  | Transconductance Amplifier                              | 70 |

|     |       | 4.2.1.4  | Measurement Buffer                                      | 70 |

|     |       | 4.2.1.5  | Non-overlapping Clock Generator                         | 70 |

|     | 4.2.2 | Layout   | of the Individual Blocks                                | 70 |

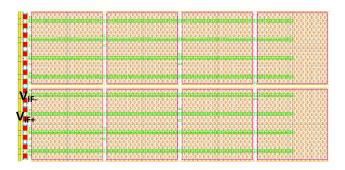

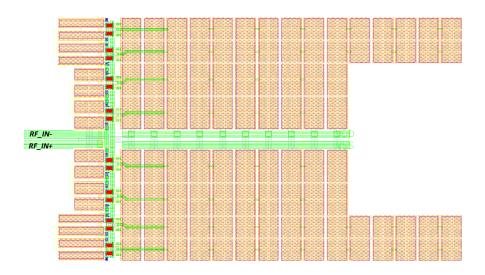

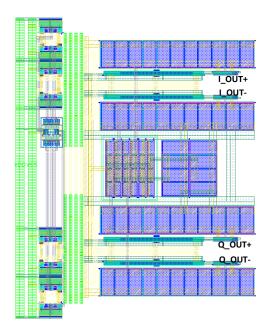

|   |     |        | 4.2.2.1              | Layout of the Eight-Path Mixer                             | 71 |

|---|-----|--------|----------------------|------------------------------------------------------------|----|

|   |     |        | 4.2.2.2              | Layout of the BBLNA                                        | 71 |

|   |     |        | 4.2.2.3              | Layout of the $g_m$ -cell                                  | 71 |

|   |     |        | 4.2.2.4              | Layout of the Eight-Phase Non-Overlapping Clock Generation | 73 |

|   |     | 4.2.3  | Post-Lay             | yout Performance                                           | 74 |

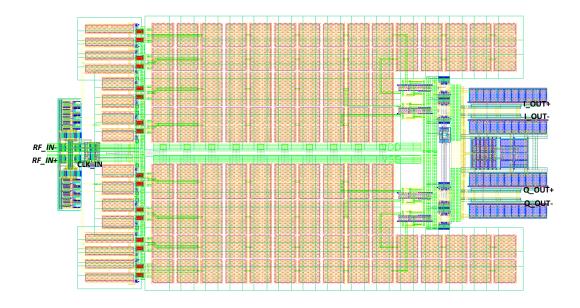

|   | 4.3 | Full-C | hip Layou            | ut                                                         | 74 |

|   | 4.4 | Conclu | usions               |                                                            | 76 |

| 5 | Mea | asurem | ent Res              | ults and Discussion                                        | 77 |

|   | 5.1 | Proce  | es Scalah            | le Architecture for Low Noise Figure Sub-Sampling Mixer-   |    |

|   | 0.1 |        |                      | End                                                        | 77 |

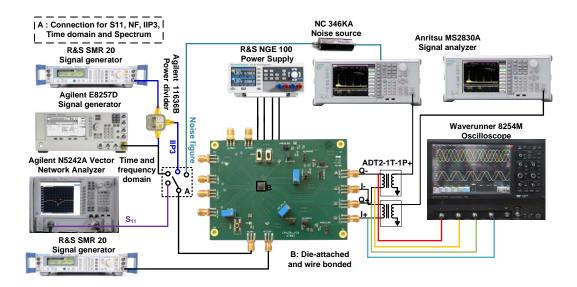

|   |     | 5.1.1  | Measure              | ement Setup                                                | 77 |

|   |     | 5.1.2  | Quadrat              | cure Down-Conversion                                       | 79 |

|   |     | 5.1.3  | Harmon               | ic Rejection and Noise Figure                              | 80 |

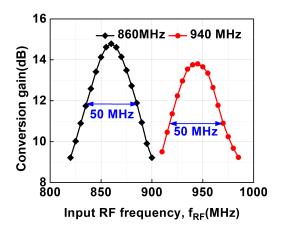

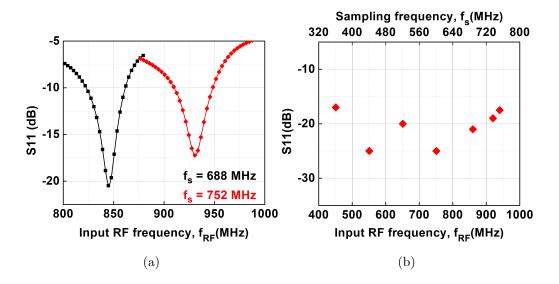

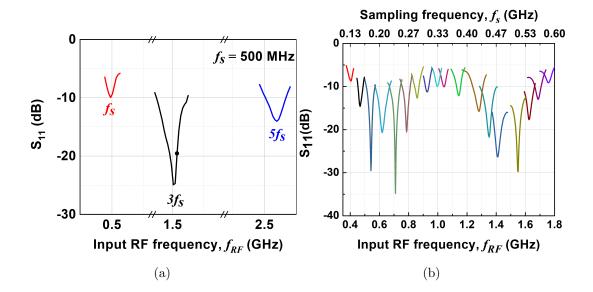

|   |     | 5.1.4  | Conversi             | ion Gain and Input Return Loss $S_{11}$                    | 82 |

|   |     | 5.1.5  | IIP <sub>3</sub> and | l Power Consumption                                        | 84 |

|   | 5.2 | Digita | lly Intens           | sive Sub-Sampling Mixer-First Direct Down-Conversion Re-   |    |

|   |     | Ü      | v                    |                                                            | 84 |

|   |     | 5.2.1  | Measure              | ement Setup                                                | 84 |

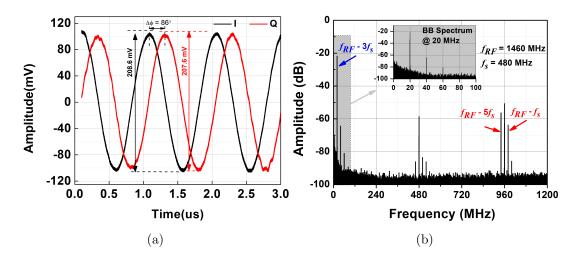

|   |     | 5.2.2  | Quadrat              | cure Down-Conversion                                       | 85 |

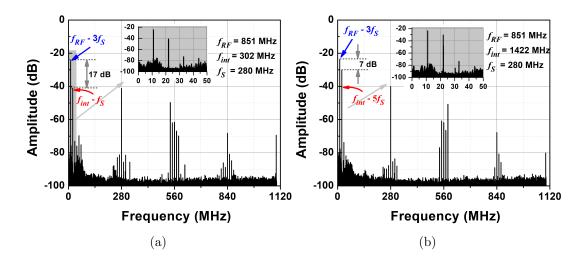

|   |     | 5.2.3  | Conversi             | ion Gain and Noise Figure                                  | 87 |

|   |     | 5.2.4  | Input R              | Return-Loss, $S_{11}$                                      | 88 |

|   |     | 5 2 5  | IIP, and             | Power Consumption                                          | 80 |

|   | 5.3   | Perfor  | mance Comparison                                                | 91  |

|---|-------|---------|-----------------------------------------------------------------|-----|

|   |       | 5.3.1   | Process Scalable Architecture for Low Noise Figure Sub-Sampling | 0.1 |

|   |       |         | Mixer-First RF Front-End                                        | 91  |

|   |       | 5.3.2   | Digitally Intensive Sub-Sampling Mixer-First Direct Down-       |     |

|   |       |         | Conversion Receiver Architecture                                | 91  |

|   | 5.4   | Concl   | usions                                                          | 94  |

| 6 | Su    | mmary   | v, Conclusions and Future Work                                  | 95  |

|   | 6.1   | Summ    | ary                                                             | 95  |

|   | 6.2   | Concl   | usions                                                          | 97  |

|   | 6.3   | Future  | e Work                                                          | 97  |

|   | D:1-1 | iograph |                                                                 | 08  |

# List of Figures

| 1.1  | (a) Global forecast of different device subscriptions (b) connected devices[1]                                                                     | 1  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Architectural evolution of the receiver RF front-end                                                                                               | 2  |

| 1.3  | Block diagram representation of an (a) ideal [2] (b) and practical software defined radio                                                          | 3  |

| 1.4  | Block diagram of the sub-sampling receiver RF front-end<br>[10] $\ \ \ldots \ \ \ldots$                                                            | 6  |

| 1.5  | Block diagram of the low noise figure sub-sampling mixer[11]                                                                                       | 7  |

| 1.6  | Block diagram of the dual-band sub-sampling receiver[9]                                                                                            | 8  |

| 1.7  | (a) Simplified architecture of a single-ended SC RF front-end (b) clock waveform (c) operation of the SC RF front-end[12]                          | 10 |

| 1.8  | Block diagram of the passive mixer-first receiver with widely tunable RF interface[13]                                                             | 11 |

| 1.9  | Block diagram of LNA first wideband receiver architecture<br>[16]                                                                                  | 12 |

| 1.10 | Block diagram of the proposed process scalable sub-sampling mixer-first RF front-end                                                               | 16 |

| 1.11 | Block diagram of the proposed sub-sampling direct down-conversion mixer-first receiver architecture                                                | 17 |

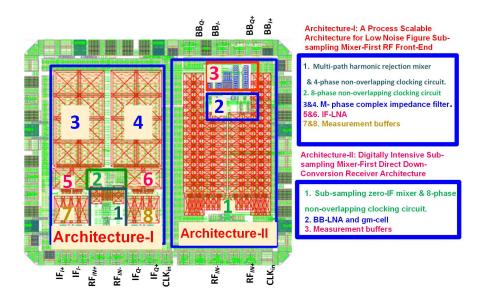

| 1.12 | (a) Full-chip layout, (b) microphotograph of the bare die and photograph of the test PCB                                                           | 19 |

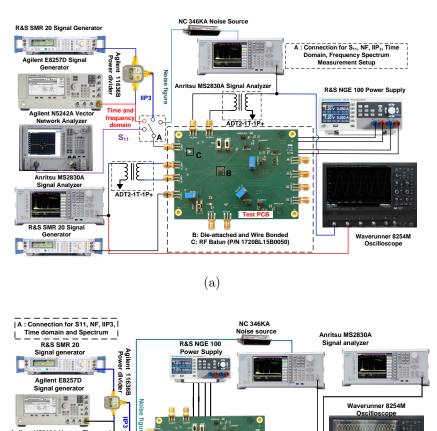

| 1.13 | Test chip measurement setup (a) architecture-I, (b) architecture-II                                                                                | 20 |

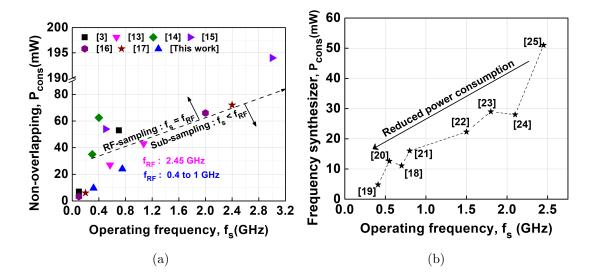

| 2.1  | Power consumption of the (a) non-overlapping multi-phase clock generation, distribution circuits, (b) sampling frequency synthesizers versus their |    |

|      | operating frequency                                                                                                                                | 24 |

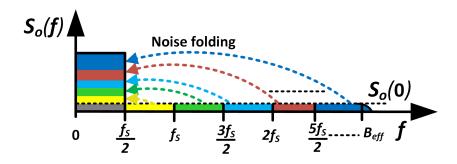

| 2.2  | Noise folding in the sub-sampling down conversion                                                                                                                                                                                                                                 | 26 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3  | Single path sub-sampling mixer                                                                                                                                                                                                                                                    | 27 |

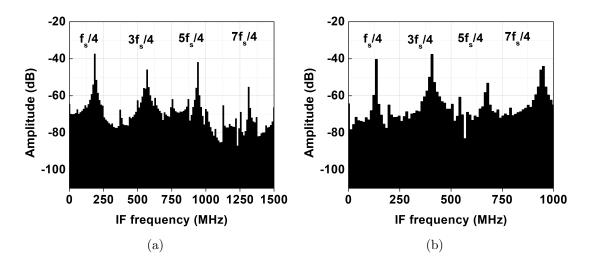

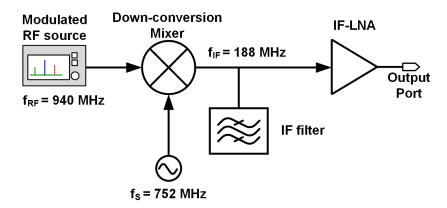

| 2.4  | Single path sub-sampling mixer IF output spectrum (a) for an $f_{RF}=940$ MHz and $f_s$ of 752 MHz (k = 2), and (b) for an $f_{RF}=940$ MHz and $f_s$ of 537 MHz (k = 3)                                                                                                          | 28 |

| 2.5  | Four-path harmonic rejection sub-sampling mixer                                                                                                                                                                                                                                   | 29 |

| 2.6  | Four path mixer IF output spectrum (a) for an $f_{RF}$ of 940 MHz and $f_s$ of 752 MHz (k = 2), and (b) for an $f_{RF}$ of 940 MHz and $f_s$ of 537 MHz (k = 3).                                                                                                                  | 31 |

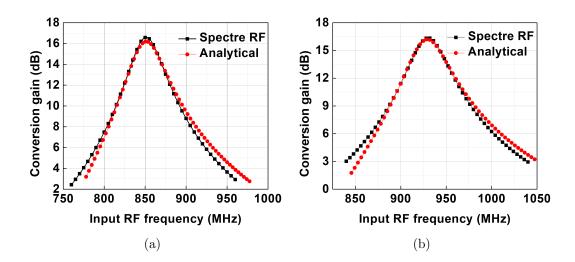

| 2.7  | RF front-end conversion gain (a) for an $f_s$ of 688 MHz and $f_{RF}$ of 860 MHz and (b) for an $f_s$ of 752 MHz and $f_{RF}$ of 940 MHz                                                                                                                                          | 32 |

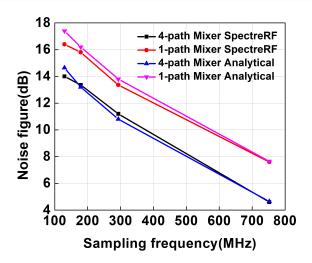

| 2.8  | Noise figure of a single path and four path mixer for different sampling frequencies for $f_{RF}=940~\mathrm{MHz}$                                                                                                                                                                | 34 |

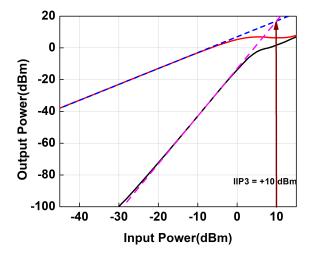

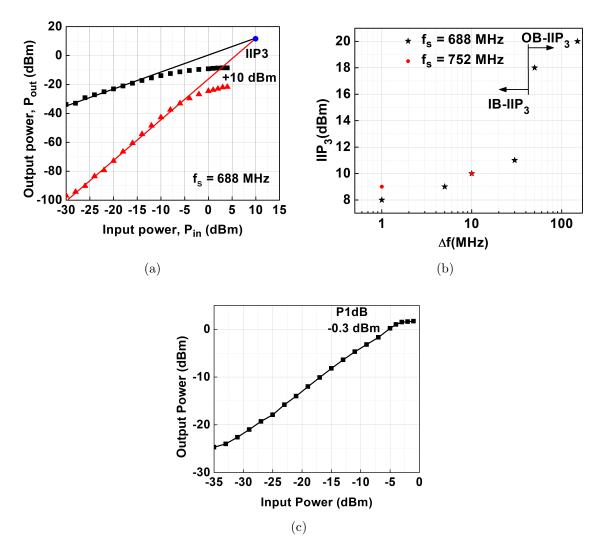

| 2.9  | IIP <sub>3</sub> of the proposed RF front-end for an $f_{RF}$ of 860 MHz, the second tone is at a 10 MHz offset and $f_s$ of 688 MHz                                                                                                                                              | 35 |

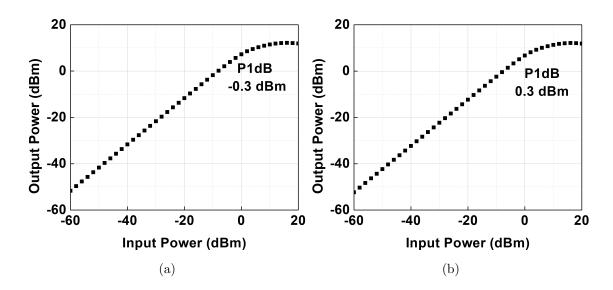

| 2.10 | P1dB of the RF front-end (a) for an $f_s$ of 688 MHz and $f_{RF}$ of 860 MHz and (b) for an $f_s$ of 752 MHz and $f_{RF}$ of 940 MHz                                                                                                                                              | 36 |

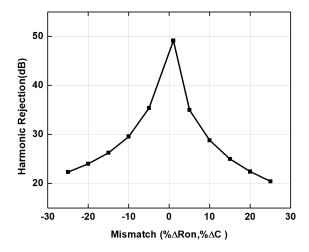

| 2.11 | Harmonic rejection versus mismatches                                                                                                                                                                                                                                              | 36 |

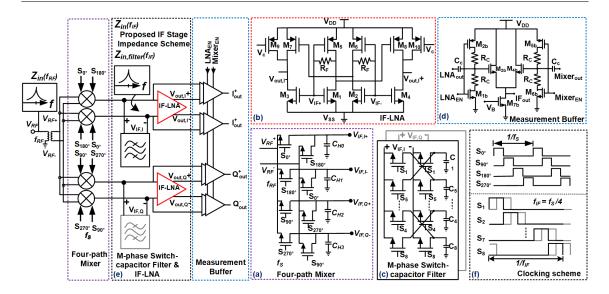

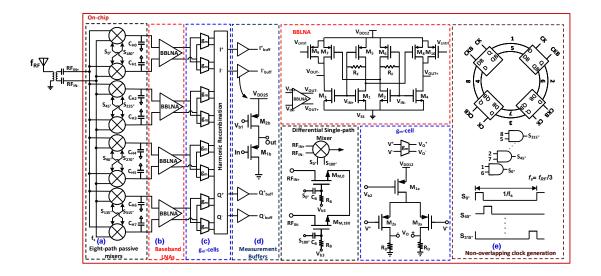

| 2.12 | Different building blocks of the RF front-end and their circuit topologies:  (a) four-path mixer (b) IF-LNA (c) M-phase switch-capacitor filter (d) measurement buffer along with (e) impedance matching scheme and (f) clocking scheme                                           | 37 |

| 2.13 | Input impedance of the IF stage switch-capacitor filter for 188 MHz sampling frequency.                                                                                                                                                                                           | 38 |

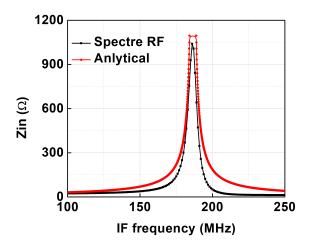

| 2.14 | The input impedance of the sub-sampling mixer first RF front-end for an $f_{RF}$ of 860 MHz and $f_s$ of 688 MHz, showing the (a) real part and (b) imaginary part. Input impedance for an $f_{RF}$ of 940 MHz and $f_s$ of 752 MHz, showing (c) the real part (d) imaginary part | 39 |

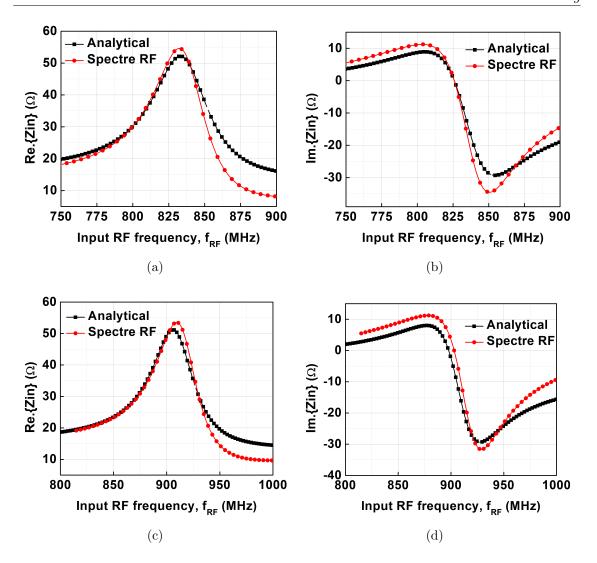

| 2.15 | Input impedance of the front-end from Eq. (2.14)(a) $ Z_{in}(\omega_{RF}) $ for varying IF stage impedance $ Z_{in}(\omega_{IF}) $ , (b) $ Z_{in}(\omega_{RF}) $ for varying $C_H$                             | 40 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | Block diagram of the proposed sub-sampling mixer-first RF front-end for EVM simulation                                                                                                                         | 41 |

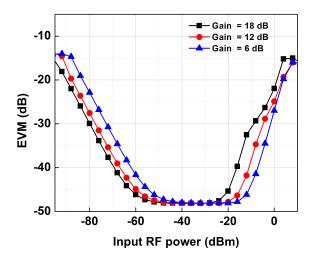

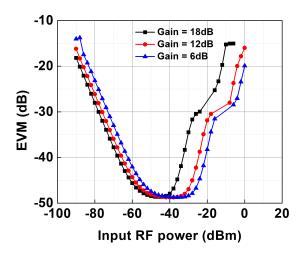

| 2.17 | System level EVM of the complete RF front-end for varying input power levels and gain of the IF-LNA                                                                                                            | 42 |

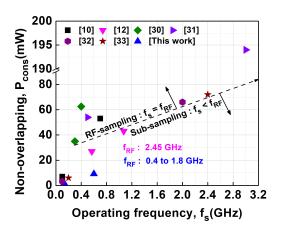

| 3.1  | Power consumption of the non-overlapping clock generation circuits                                                                                                                                             | 44 |

| 3.2  | Comparison of VCO power consumption with respect to RF sampling, subsampling, and quarter-rate sub-sampling                                                                                                    | 45 |

| 3.3  | Block diagram of the proposed quarter-rate sub-sampling direct down-conversion mixer-first RF front-end                                                                                                        | 46 |

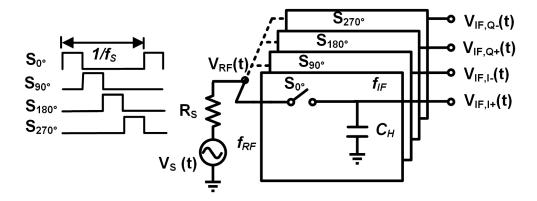

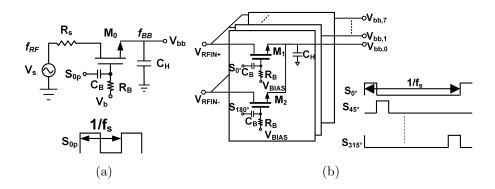

| 3.4  | (a) Single path switch-capacitor mixer, (b) eight path sub-sampling mixer and non-overlapping clocking scheme with $12.5\%$ duty cycle[29]                                                                     | 47 |

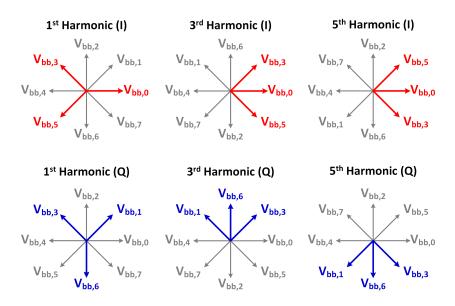

| 3.5  | Vector representation of the baseband voltages of the eight-path mixer with respect to fundamental, $3^{rd}$ and $5^{th}$ harmonics of the sampling frequency, $f_s$                                           | 48 |

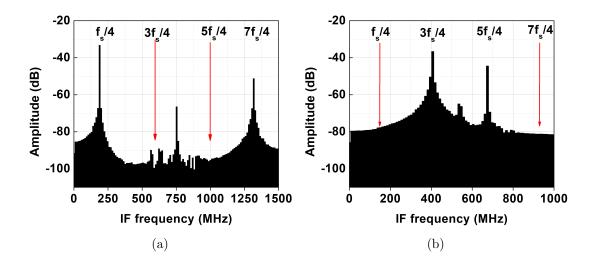

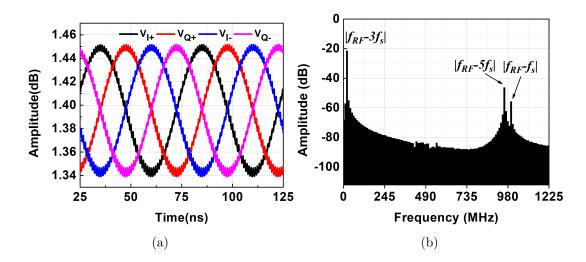

| 3.6  | Proposed RF front-end (a) time domain output waveforms, and (b) in-phase output spectrum for an $f_{RF}$ of 1490 MHz, $f_s$ of 490 MHz                                                                         | 49 |

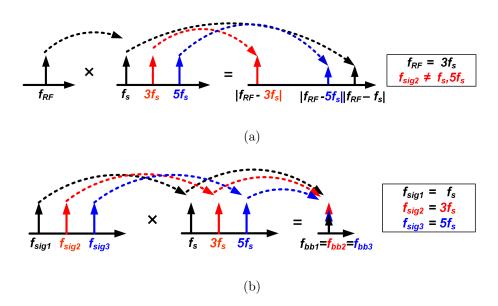

| 3.7  | Harmonic down-conversion of the mixer (a) for signal present at the $3^{rd}$ harmonic of the sampling frequency, $f_s$ , (b) for signal present at the corresponding harmonic of the sampling frequency, $f_s$ | 50 |

| 3.8  | Conversion gain of the RF front-end for an $f_{RF}$ of 1470 MHz and $f_s$ of 490 MHz                                                                                                                           | 51 |

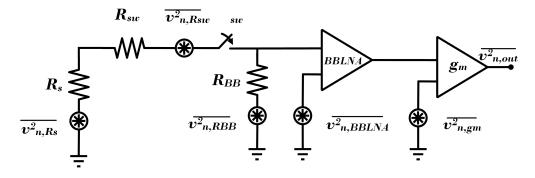

| 3.9  | Equivalent noise model of the proposed RF front-end                                                                                                                                                            | 51 |

| 3.10 | IIP <sub>3</sub> of the proposed RF front-end for an $f_{RF}$ of 1470 MHz, the second tone is at a 10 MHz offset and $f_s$ of 490 MHz                                                                          | 53 |

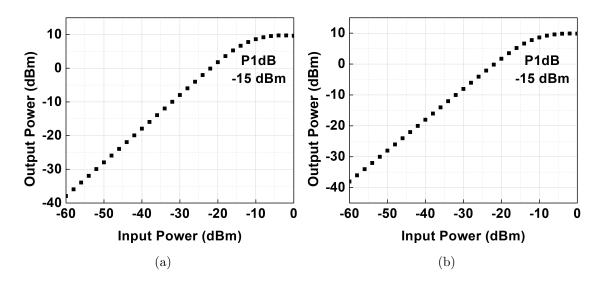

| 3.11 | P1dB of the RF front-end (a) for an $f_s$ of 313.3 MHz and $f_{RF}$ of 940 MHz and (b) for an $f_s$ of 490 MHz and $f_{RF}$ of 1472 MHz                                                                  | 53 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

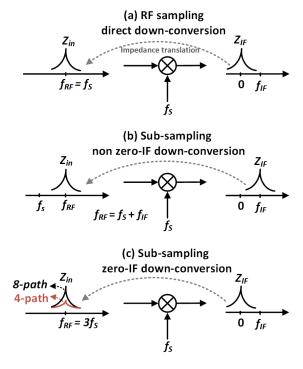

| 3.12 | Impedance translation for (a) RF sampling zero-IF down-conversion, (b) sub-sampling non-zero-IF down-conversion, and (c) proposed sub-sampling zero-IF down-conversion                                   | 54 |

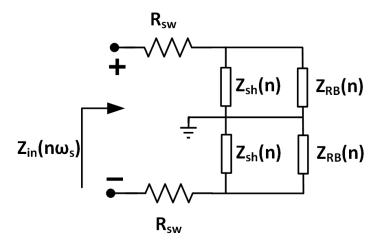

| 3.13 | Input impedance model for differential N-path mixer[29]                                                                                                                                                  | 55 |

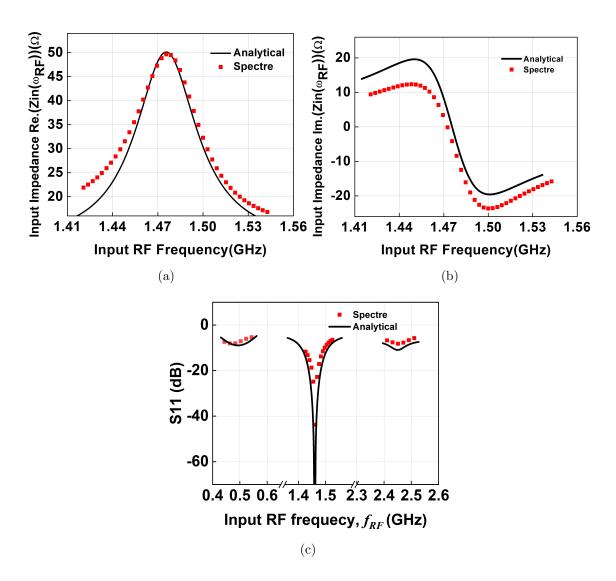

| 3.14 | The input impedance of the sub-sampling mixer-first direct down-conversion RF front-end for an $f_{RF}$ of 1470 MHz and $f_s$ of 490 MHz, showing the (a) real part, (b) imaginary part and (c) $S_{11}$ | 56 |

| 3.15 | Block level model of the RF front-end                                                                                                                                                                    | 57 |

| 3.16 | System level EVM of the RF front-end for varying input RF power and BBLNA gain                                                                                                                           | 58 |

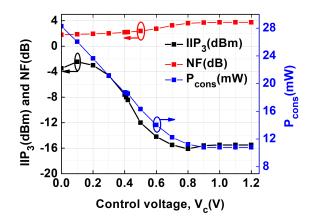

| 4.1  | $IIP_3$ , noise figure and power consumption of the IF-LNA with respect to control voltage $V_c$                                                                                                         | 61 |

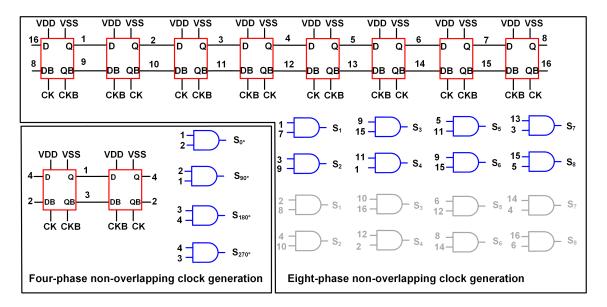

| 4.2  | Four and eight phase non-overlapping clock scheme                                                                                                                                                        | 62 |

| 4.3  | Layout of the four-path switch-capacitor mixer                                                                                                                                                           | 63 |

| 4.4  | Layout of the IF-LNA                                                                                                                                                                                     | 64 |

| 4.5  | Layout of the M-path filter                                                                                                                                                                              | 65 |

| 4.6  | Layout of the (a) four-phase non-overlapping clock generator and (b) eight-phase clock generator                                                                                                         | 65 |

| 4.7  | Layout of the full architecture                                                                                                                                                                          | 65 |

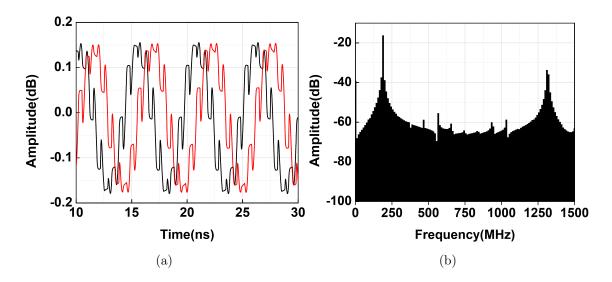

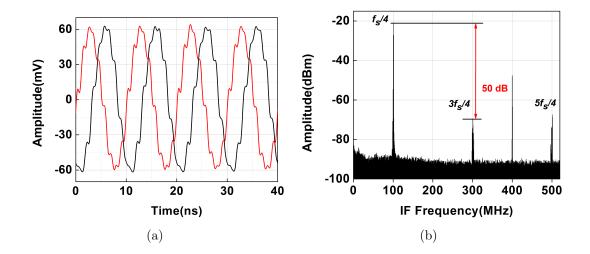

| 4.8  | (a) Transient IF outputs, (b) spectrum of the in-phase output                                                                                                                                            | 66 |

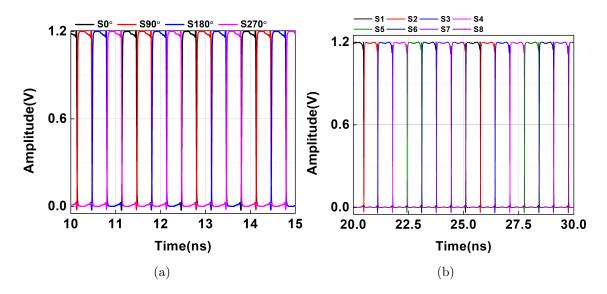

| 4.9  | Post layout outputs of the (a) four phase and (b) eight-phase non-overlapping clock                                                                                                                      | 67 |

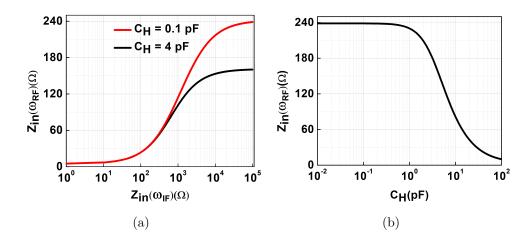

| 4.10 | ceiver architecture and their circuit topologies: (a) eight-path passive mixer                                                                                  |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | (b) BBLNA (c) $g_m$ -cell (d) measurement buffer and (e) non-overlapping                                                                                        |    |

|      | clocking scheme                                                                                                                                                 | 68 |

| 4.11 | Layout of the eight-path mixer                                                                                                                                  | 71 |

| 4.12 | Layout of the BBLNA                                                                                                                                             | 72 |

| 4.13 | Layout of the $g_m$ -cell and measurement buffer                                                                                                                | 72 |

| 4.14 | Layout of the eight-phase clock generation circuit                                                                                                              | 73 |

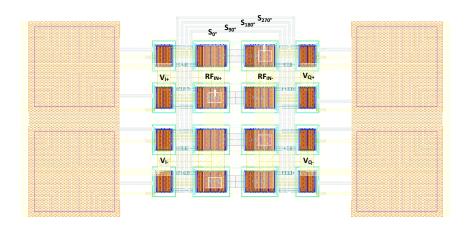

| 4.15 | Layout of the full architecture                                                                                                                                 | 73 |

| 1 16 | (a) Transient base-band outputs (b) spectrum of the in-phase output and                                                                                         |    |

| 4.10 | (c) eight-phase non-overlapping clock                                                                                                                           | 75 |

| 4.17 | Layout of the full-chip                                                                                                                                         | 76 |

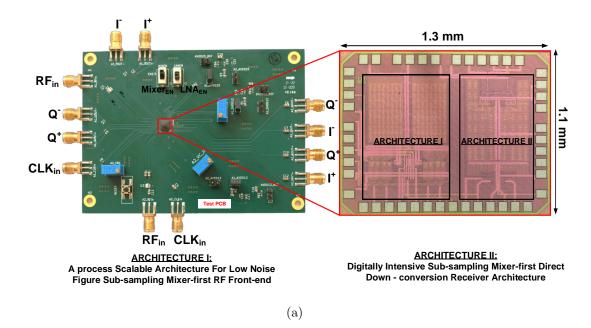

| 5.1  | (a) Fabricated IC micro-photograph and the test PCB (b) measurement setup                                                                                       | 78 |

| 5.2  | Measured (a) time domain output and corresponding frequency spectrum at IF for an $f_{RF}$ of 501 MHz, and $f_s$ of 400 MHz                                     | 79 |

| 5.3  | Measured frequency spectrum at IF (a) for an $f_{RF}$ of 860 MHz, and $f_s$ of 688 MHz, and (b) for an $f_{RF}$ of 940 MHz, and $f_s$ of 752 MHz                | 80 |

| 5.4  | Measured IF harmonic rejection for varying input RF frequency and its corresponding sampling frequency                                                          | 80 |

| 5.5  | Measured noise figure and conversion gain with respect to input RF frequency and its corresponding sampling frequency                                           | 81 |

| 5.6  | Measured conversion gain of the RF front-end for an $f_{RF}$ of 860 MHz and 940 MHz                                                                             | 81 |

| 5.7  | (a) Measured $S_{11}$ for an $f_{RF}$ of 860 MHz and 940 MHz (b) Measured $S_{11}$ with respect to input RF frequency and its corresponding sampling frequency. | 82 |

| 5.8  | Measured IIP <sub>3</sub> (a) at an $f_{RF}$ of 860 MHz, second tone is at a 10 MHz offset                                                                                                                                                             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and (b) for varying $\Delta f$ for both the 860 MHz and 940 MHz bands and (c)                                                                                                                                                                          |    |

|      | Measured P1 dB for an $f_{RF}$ of 860 MHz and $f_s$ of 688 MHz                                                                                                                                                                                         | 83 |

| 5.9  | Measurement setup                                                                                                                                                                                                                                      | 85 |

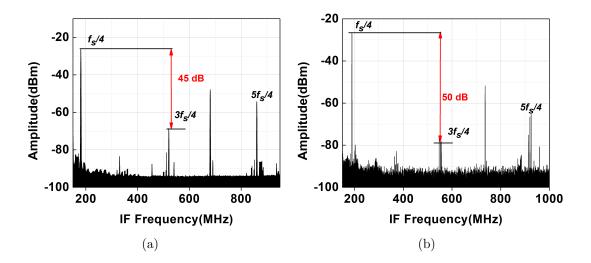

| 5.10 | Measured (a) transient base-band in-phase and quadrature outputs down-converted to 1 MHz for an $f_{RF}$ of 1462 MHz and $f_s$ of 487 MHz and (b) spectrum at the base-band for an $f_{RF}$ of 1460 MHz and $f_s$ of 480 MHz                           | 86 |

| 5.11 | Measured base-band output spectrum of the RF front-end for an $f_s$ of 280 MHz and $f_{RF}$ of 851 MHz in the presence of interferer, $f_{int}$ at the (a) fundamental, and (b) fifth harmonic of $f_s$                                                | 87 |

| 5.12 | Measured conversion gain for an $f_{RF}$ of 1470 MHz and $f_s$ of 490 MHz                                                                                                                                                                              | 87 |

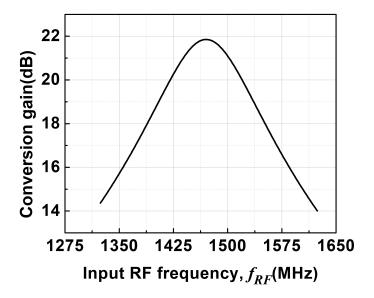

| 5.13 | Measured conversion gain and noise figure with respect to input RF frequency, $f_{RF}$ and its corresponding sampling frequency, $f_s$                                                                                                                 | 88 |

| 5.14 | (a) Measured $S_{11}$ for an input RF frequency, $f_{RF}$ of 1.5 GHz, sampling frequency, $f_s$ of 500 MHz and (b) measured $S_{11}$ with respect to $f_{RF}$ and its corresponding $f_s$                                                              | 89 |

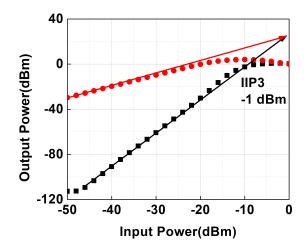

| 5.15 | Measured IIP <sub>3</sub> (a) at an $f_{RF}$ of 1472 MHz, with the second tone at 1 MHz offset and $f_s$ of 490 MHz and (b) for varying $\Delta f$ for an $f_{RF}$ of 1460 MHz and (c) Measured P1 dB for an $f_{RF}$ of 1472 MHz and $f_s$ of 490 MHz | 90 |

## List of Tables

| 1.1 | Performance summary of the state-of-the-art RF front-ends present in the    |    |

|-----|-----------------------------------------------------------------------------|----|

|     | literature                                                                  | 14 |

| 2.1 | Parameters of IEEE 802.15.4 Standard                                        | 26 |

| 2.2 | Block-level specification of the proposed receiver RF front-end for system- |    |

|     | level EVM simulation                                                        | 41 |

| 2.3 | Performance summary of the proposed RF front-end                            | 42 |

| 3.1 | Block level specifications of the proposed sub-sampling direct down-        |    |

|     | conversion receiver                                                         | 57 |

| 3.2 | Performance summary of the proposed RF front-end                            | 58 |

| 4.1 | Post-layout performance summary of the proposed RF front-end                | 67 |

| 4.2 | Post-layout performance summary of the digitally intensive direct down-     |    |

|     | conversion receiver                                                         | 74 |

| 5.1 | Performance summary and comparison with the state of the art RF front-ends  | 92 |

| 5.2 | Performance summary and comparison with the state of the art RF front-ends  | 93 |

#### List of Abbreviations

LO Local oscillator

NF Noise figure

CG Conversion gain

P1dB 1dB compression point

IIP3 Input third order intercept point

HTF Harmonic transfer function

SNR Signal-to-noise-ratio

SS Sub-sampling

QRSS Quarter-rate sub-sampling

LNA Low noise amplifier

RF Radio frequency

IF Intermediate frequency

BB Base band

HR Harmonic rejection

HRR Harmonic rejection ratio

LR-WN Low rate wireless network

EVM Error vector magnitude

ADC Analog to digital converter

DAC Digital to analog converter

PA Power amplifier

MOS Metal oxide semiconductor

CMOS Complementary metal oxide semiconductor

SDR Software-defined-radio

S/H Sample and hold

Q Quality factor

FIR Finite impulse response

WLAN Wireless local area network

NPF N-path filter

TIA Trans impedance filter

CT continuous time

DT Discrete time

SC Switch-capacitor

I/ Q In-phase and Quadrature phase

${

m LNTA}$  low noise trans-conductance amplifier

### Chapter 1

#### Introduction

#### 1.1 Trends in Wireless Communications

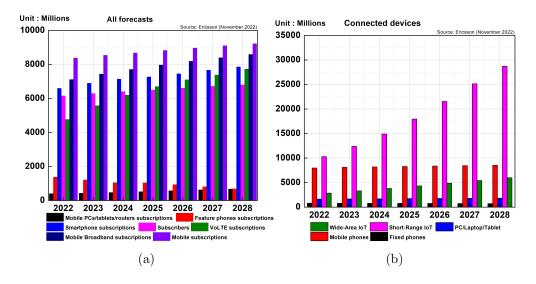

Global mobile subscriptions are forecasted to reach 9.2 billion by the year 2028 as shown in Fig. 1.1(a). The fifth-generation technology-based connections are expected to occupy 54 % of the share of mobile traffic and 80 % of fixed wireless access (FWA) connections[1]. The FWA provides a high-speed data transfer to the customers over the air with the help of fixed base stations connected to a network. These base stations offer high-speed wireless connectivity to remote areas without proper infrastructure. In addition, the number of connected IoT devices over mobile networks is around 2.7 billion, and it is projected to reach 5.5 billion in 2028, as shown in Fig. 1.1(b). These statistics reveal the need for flexible radio with a programmable or re-configurable RF front-end to support increased spectrum congestion and multi-band operation to accompany multiple standards using a single receiver. The need for multi-standard operation has led researchers to propose the idea of software-defined radio(SDR).

Figure 1.1: (a) Global forecast of different device subscriptions (b) connected devices[1]

The concept of SDR is placing the analog-to-digital converter(ADC) just after the antenna receiver[2] and digitizing all the received bands. However, the ADC operating at high frequency imposes impractical power constraints on the ADC[3]. The alternative to an SDR is a flexible radio that supports a multi-band operation with less power dissipation and minimum hardware is the closest possible version of an SDR, which is a digitally intensive receiver. A switch-capacitor based receiver RF front-end provides programmable wide-band operation and consumes very low power makes it digitally intensive RF front-end.

This chapter introduces digitally intensive switch-capacitor RF front-ends in Section 1.2, followed by the classification of the RF front-end architectures based on down-conversion frequency in Section 1.3. Then a brief literature survey on the sub-sampling and RF sampling switch-capacitor RF front-ends is presented in Section 1.4. Afterwards, Section 1.5 presents the research gaps among the reported RF front-ends architectures and thesis objectives are presented. The concept of proposed sub-sampling digitally intensive mixer-first RF front-ends is explained in Section 1.6. Thesis contributions and organization of the thesis are presented in Section 1.7 and Section 1.8, respectively.

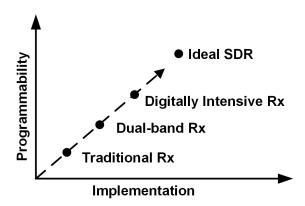

Figure 1.2: Architectural evolution of the receiver RF front-end

#### 1.2 Digitally Intensive Switch-Capacitor RF Front-Ends

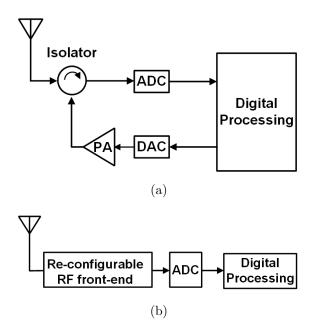

The quest for software-defined radio has led researchers to propose various receiver architectures, from traditional single-band radios to digitally intensive architectures, shown in Fig. 1.2. A conceptual representation of an ideal SDR contains an analog-to-digital converter(ADC) and digital-to-analog converter(DAC) just after the antenna before base-band processing as shown in Fig. 1.3(a). To perform the task, it is necessary that the

ADC in the SDR must have extraordinary specifications. In addition, ADC with such high dynamic range and other specifications dissipates hundreds of watts of power for conversion[4]. Therefore, a flexible or re-configurable radio receiver that receives any channel at an arbitrary frequency with less power dissipation and minimum hardware is the closest possible version of an ideal SDR as shown in Fig. 1.3(b).

Figure 1.3: Block diagram representation of an (a) ideal [2] (b) and practical software defined radio

The CMOS technology scaling has improved the switching characteristics of a MOS transistor[5]. The rise time and fall time of the transistor switches in the advanced nanometer design are in the order of tens of picoseconds. These rise and fall times offer good timing accuracy to support operation at high frequencies. In addition, modern lithography techniques offer a wide range of capacitor ratios[6]. These advancements have benefited from realizing re-configurable RF front-ends using switch-capacitor mixers and filters. A switch-capacitor mixer-first RF front-end provides performance tunability over a wide frequency range by tuning sampling frequency. This property of switch-capacitor RF front-ends makes them digitally intensive. Therefore, a digitally intensive switch-capacitor radio architecture is the closest equivalent to an ideal software-defined radio(SDR) as shown in Fig. 1.3(b). There are switch-capacitor RF front-ends proposed in the literature which are based on RF sampling down-conversion and sub-sampling. The down-conversion principle of both the RF sampling and sub-sampling based switch-capacitor RF front-ends and the differences among the implementation are explained below.

#### 1.2.1 RF Sampling Based Switch-Capacitor RF Front-Ends

RF sampling-based switch-capacitor front-ends require a sampling frequency greater than or equal to the input RF frequency to implement down-conversion and filtering using N-path mixers and filters, respectively. The N-path implementation of the mixer and filters have advantages in terms of noise figure, tunable high-Q bandwidth, and impedance matching. However, the N-path topology requires precise N-phase non-overlapping clocks for operation, and to generate precise multi-phase non-overlapping clocks, clock dividers are required. To generate non-overlapping clocks with a frequency,  $f_s$ , the dividers require a reference clock frequency of at least  $Nf_s/2$ . Hence, the power consumption of these non-overlapping clock generation and distribution circuitry increases with the increasing  $f_{RF}$  since the corresponding sampling frequency also increases. In addition, the stringent jitter requirements increase the power consumption of the frequency synthesizers at high frequencies. Therefore, the power consumption of the clock generation circuit is no longer negligible since it increases with the input RF frequency  $f_{RF}$ .

#### 1.2.2 Sub-Sampling Based Switch-Capacitor RF Front-Ends

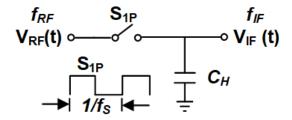

Sub-sampling down-conversion requires a sampling frequency less than the input RF frequency leading to the reduced power consumption of the frequency synthesizer, non-overlapping clock generation, and distribution circuitry[7, 8]. The theory of band-pass sampling states that "for uniform sampling states that the signal can be reconstructed if the sampling rate is at least  $f_s = \frac{2f_u}{n}$ , where 'n' is the largest integer within  $\frac{f_u}{BW}$ [7]". Where ' $f_u$ ' is the maximum frequency and 'BW' is the bandwidth of the input band-pass signal. This sampling condition is analogous to the low pass sampling, which has a condition for sampling  $f_s > 2f_u$ , where the input signal's bandwidth is  $[0, f_u]$ . On the other hand, the quadrature sampling case of band-pass sampling states that if the sampling frequency is selected from Eq. 1.1, the input signal gets down-converted to IF, and the alternative samples at the output are in quadrature.

$$f_s = \frac{4f_{RF}}{2k+1}; k = 0, 1, 2, 3 \dots$$

$$f_{IF} = \min(|f_{RF} - nf_s|) = f_s/4$$

(1.1)

Where,  $f_{IF}$  represents the intermediate frequency, 'n' represents the harmonic of the

sampling frequency.

The sub-sampling receivers proposed in the literature have emphasized the implementation of down-conversion at both the RF and IF stages down-conversion. These implementations show that sub-sampling down-conversion is a good alternative to RF sampling down-conversion for implementing re-configurable switch-capacitor mixer-first RF front-ends for low-power and wide-frequency band applications. However, the sub-sampling down-conversion is not a popular choice for implementing in mixer-first receivers due to the disadvantage of high noise figure from inherent noise folding and lack of RF port impedance matching because of non-zero IF down-conversion.

#### 1.3 Problem Definition

As explained in Section 1.2.1, RF sampling-based RF front-end requires a sampling frequency greater than the input RF frequency hence it increases the power budget of the receiver. On the other hand, sub-sampling down-conversion has the advantage of operating at a low sampling frequency, thereby reducing the power consumption of clock generation, distribution and frequency synthesizer circuits. However, the sub-sampling down-conversion is not a popular choice for implementing in mixer-first receivers since the sub-sampling down-conversion is inherently heterodyne in nature and high noise figure [9, 10]. As a consequence of non-zero IF down-conversion, the passive mixer transparency property can not be exploited for providing impedance matching at the RF port by impedance translation. Therefore, it is required to address the problems of sub-sampling down-conversion, such as non-zero-IF down-conversion, high noise figure and lack of impedance matching to make it a suitable alternative to RF sampling-based receivers front-ends.

#### 1.4 Literature Survey

In recent years, there has been increasing research interest in re-configurable RF front-ends with frequency translation features. The advancements in CMOS technology scaling improved the switching property of the MOS transistor; hence the switch-capacitor circuits, such as passive mixers and filters, support wide-band operation. In a receiver, employing switch-capacitor circuits at the RF facilitates programmable multi-band operation using a single RF front-end. This section gives an overview of the existing switch-capacitor-

based sub-sampling RF front-end architectures [9–11] along with the RF sampling-based switch-capacitor RF front-end architectures [5], reported in the literature.

#### 1.4.1 Switch-Capacitor Sub-Sampling RF Front-Ends

Sub-sampling down-conversion employs a sampling frequency which is lower than twice the highest frequency of the input RF signal but higher than two times the input RF signal bandwidth. The sub-sampling down-conversion mixer employing a sampling frequency of  $f_s$ , translates the input RF signal with a frequency  $f_{RF}$  to  $\frac{f_s}{4}$ ,  $\frac{3f_s}{4}$ ,  $\frac{5f_s}{4}$ ,... etc. In the literature, there are few sub-sampling receivers reported, such as the sub-sampling down-conversion receiver RF front-end architecture [10], which employs two-stage down-conversion to zero frequency down-conversion, the current integrating sub-sampling mixer translates the IF frequency to base-band using a  $g_m$ -cell, four-path sub-sampling down-conversion mixer and complex filter[11], and the dual-band down-conversion receiver employed two-stage down-conversion schemes for each band[9].

Figure 1.4: Block diagram of the sub-sampling receiver RF front-end[10]

#### 1.4.1.1 Heterodyne Sub-Sampling Receiver in 0.18- $\mu m$ CMOS

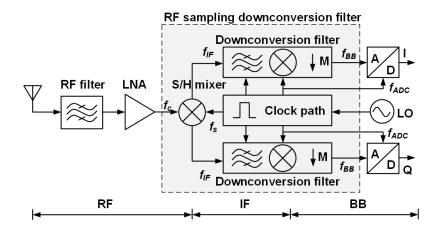

The heterodyne switch-capacitor sub-sampling receiver reported in [10] employed a two-stage discrete-time quadrature down-conversion mixing scheme. The RF front-end contains an RF filter, a tuned LNA, and a switch-capacitor sub-sampling mixer followed by a switch-capacitor decimation filter, shown in Fig. 1.4. The sub-sampling down-conversion receiver architecture is designed for 2.4 GHz IEEE 802.11b/g standard wireless local area network (WLAN) applications in 0.18  $\mu$ m CMOS. The input RF signal received by the

antenna passes through an RF filter which filters the image of the RF signal, the LNA amplifies the output of the filter, and then it is fed to a single-path sample-hold(S/H) quadrature down-conversion mixer. As proposed in [10], the S/H mixer translates the input RF signal of 2.4 GHz to an intermediate frequency (IF) depending upon the selection of sampling frequency given by Eq. 1.1. For example, the RF signal gets translated to an IF of 268 MHz for a sampling frequency of 1.072 GHz and to an IF of 142 MHz for a sampling frequency of 547.5 MHz. The selection of low sampling frequency, such as 547.5 MHz, translates the input to low IF compared to 1.072 GHz. However, selecting a low sampling frequency of 567.5 MHz translates the copies of RF down-conversions closer compared to the 1.072 GHz, requiring a high-Q RF filter. The output of the mixer is further down-converted to baseband by the switch-capacitor decimation filter. The sampling frequency of the filter is 89.5 MHz, which is obtained by dividing the mixer clock frequency by 24. This way, the decimation filter offered band-pass filtering and down-conversion using decimation. However, the reported sub-sampling receiver does not provide any gain hence it has a high noise figure of 44 dB, an IIP<sub>3</sub> of +5.5 to +13.5, and low bandwidth of 20 MHz only.

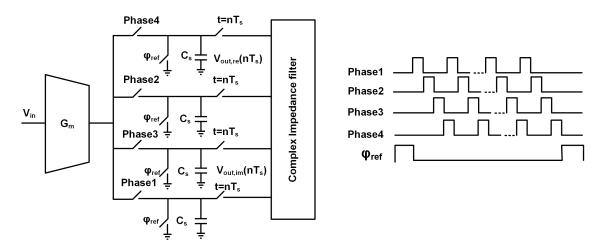

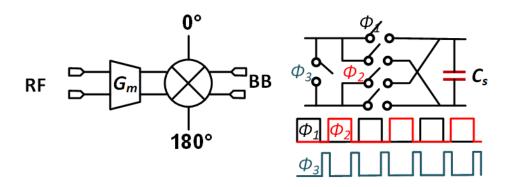

Figure 1.5: Block diagram of the low noise figure sub-sampling mixer[11]

#### 1.4.1.2 A Low Noise Quadrature Sub-Sampling Mixer

A current-mode sub-sampling down-conversion technique is presented in [11]. The current-mode mixer down-converts the input RF/IF signal to IF/BB frequency. The mixer architecture consists of a  $G_m$ -cell followed by a four-path switch-capacitor mixer and complex IIR filter as shown in Fig. 1.5. The  $G_m$ -cell transforms the input voltage

signal to current, and the switch-capacitor mixer sample the current instead of voltage onto the capacitors. The  $G_m$ -cell, along with the current integrating mixer, introduces a low pass sinc-response. The non-overlapping clock scheme of the mixer samples the alternative samples to real and imaginary channels with a time interval of  $\frac{T}{4}$ . Hence, quadrature down-conversion is achieved in the proposed scheme by introducing a time delay of  $t_i$  between the samples, given by Eq. 1.2. To improve the selectivity, the input current is integrated N-times onto the capacitors, which resembles a bandpass FIR filter. In the end, the output of the sub-sampler is further translated to a desired frequency by decimating the signal.

$$t_i = (\frac{n}{2} \pm \frac{T}{4}), \text{ where n=0, 1, 2, 3..etc}$$

(1.2)

The down-conversion mixer architecture is implemented in  $0.8\mu m$  BiCMOS technology. The measured noise figure of the sampler is 10 dB at an output frequency of 13.1 KHz. The main drawback of the work is the high noise figure even employing a  $G_m$ -cell at the input of the sampler. In addition, the  $G_m$ -cell limits the bandwidth of the sampler and the linearity of the mixer.

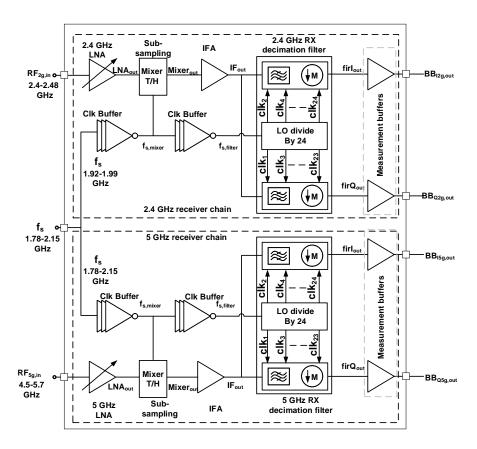

Figure 1.6: Block diagram of the dual-band sub-sampling receiver[9]

# 1.4.1.3 A Sub-Sampling Dual-Band Tunable Gain Receiver in 65-nm CMOS

A dual-band sub-sampling receiver with a bandwidth of 77 MHz and error vector magnitude(EVM) of -40 dB is proposed for WLAN application in [9]. The dual-band receiver consists of identical sub-blocks and sub-sampling down-conversion employed for down-conversion as shown in Fig. 1.6. The performance of the sub-sampling receiver chain is demonstrated for both the 2.4 GHz and 5 GHz applications. The proposed architecture consists of a tunable LNA, single-path sub-sampling switch-capacitor down-conversion mixer, IF amplifier (IFA) and a switch-capacitor decimation filter. The tunable LNA amplifies the incoming RF signal and provides the required 50  $\Omega$  impedance matching, then the single path sub-sampling down-conversion mixer translates the LNA output to an IF frequency of  $\frac{f_s}{4}$ . The IFA further amplifies the down-converted signal, then the switch-capacitor sub-sampling filter further translates the signal to base-band frequency. The dual-band receiver has a noise figure of 11.5 - 12 dB, a variable gain of 26 - 41 dB and -21 to -8 dBm IIP<sub>3</sub>. The main disadvantages of the proposed work are high noise figure and poor IIP<sub>3</sub>.

#### 1.4.2 Switch-Capacitor RF Sampling Based RF Front-Ends

In the literature, all the mixer-first receivers employed RF sampling for down-conversion, requiring a sampling frequency greater than or equal to the input RF signal frequency. In contrast to traditional LNA first receivers, switch-capacitor-based receivers such as mixer first receivers and RF front-ends with higher order filtering and mixers [12–14] lack LNA at the RF front-end. These architectures provide higher linearity than LNA first receivers, however lack of RF gain results in a high noise figure. In addition, there are wide-band LNA first receiver architectures reported in the literature, such as [15, 16], which offer wide-band operation, low noise figure and high conversion gain, hence, they are suitable for SDR applications. However, the RF sampling based LNA-first receivers exhibit poor linearity and consume high power at the high frequencies due to low jitter clock requirement for implementing down-conversion[17]. The concept and working principle of various switched-capacitor based mixer-first and LNA-first receivers are presented below.

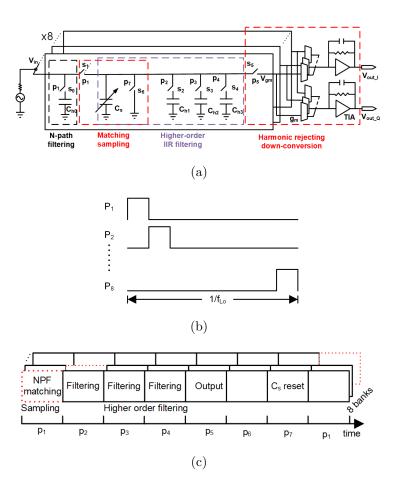

Figure 1.7: (a) Simplified architecture of a single-ended SC RF front-end (b) clock waveform (c) operation of the SC RF front-end[12]

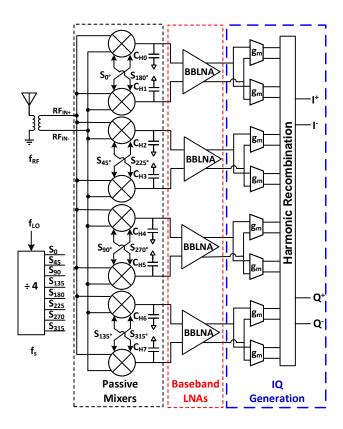

# 1.4.2.1 A Switched-Capacitor RF Front-End With Embedded Programmable High-Order Filtering

The single-ended version of the switch-capacitor receiver architecture, reported in [12], is shown in Fig. 1.7 (a). The receiver consists of eight single-ended switch-capacitor mixers for sampling and filtering, followed by base-band  $g_m$ -cells and trans-impedance amplifiers (TIAs) for harmonic rejection. The switch-capacitor front-end is driven by an eight-phase non-overlapping clock signal  $p_1$  to  $p_8$ , shown in Fig. 1.7(b). Each switch conducts for a duration of 12.5 % of  $\frac{1}{f_{LO}}$  and the sampling frequency  $f_s = 8f_{LO}$ . As depicted in Fig. 1.7(c), when  $p_1$  clock is ON, switches  $S_0$  and  $S_1$  conduct and hence the  $S_0$  switches along with  $C_{h0}$  realise an RF stage N-path filter(NPF) which attenuates out of band blocker signals. In addition, SC circuit  $s_0$  and  $C_{hs}$  provide impedance matching and sample the input RF signal. Hence,  $s_1$  and  $C_s$  convert the continuous-time (CT) input RF signal to DT domain. After sampling, the switches  $s_2$  to  $s_4$  and the history

capacitors  $C_{h1}$  to  $C_{h3}$  and  $C_{s}$ well as  $C_{s}(i)$  and  $s_{6}(i)$  realise a high-order discrete-time infinite-impulse-response (IIR) filter. After filtering the switch,  $s_{5}$  propagates the signal to the  $g_{m}$  cell input nodes. In the end, the  $g_{m}$  cells combine the outputs from all the eight switch-capacitor banks to the in-phase (I) and quadrature (Q) paths and achieve the harmonic-rejecting down-conversion. However, the amount of harmonic rejection depends on the weighing gains of the  $g_{m}$ -cells. The sampling frequency is equal to or greater than the input RF signal, and hence the power consumption of the frequency synthesizer circuit is high.

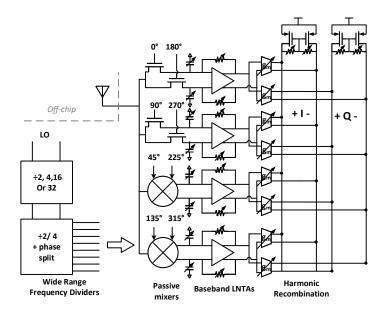

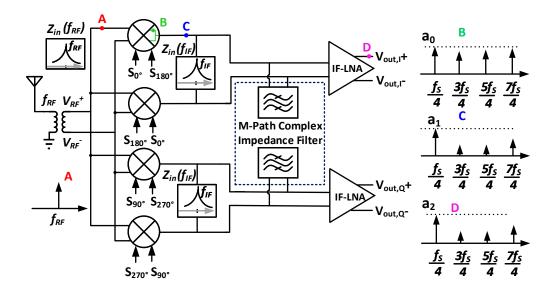

Figure 1.8: Block diagram of the passive mixer-first receiver with widely tunable RF interface[13]

# 1.4.2.2 A Passive Mixer-First Receiver With Widely Tunable RF Interface

The mixer-first direct down-conversion RF front-end [13] presented several useful concepts of switch-capacitor RF front-end interface, such as tunable input impedance matching by exploiting transparency of passive mixer switches and the input impedance of the baseband amplifier. An eight-path mixer direct down-conversion scheme is employed to translate the input RF to the base-band. These eight-path outputs are amplified by BBLNAs and recombined using  $g_m$ -cells to obtain quadrature down-conversion and harmonic rejection, shown in Fig. 1.8. However, it did not discuss the idea of direct down-conversion using harmonics of  $f_s$  and its consequences on the noise figure, conversion gain

and RF port impedance matching. In addition, this mixer-first receiver front-ends also employs RF sampling, requiring a sampling frequency greater than the input RF signal frequency, leading to the increased power consumption of clock generation circuits.

#### 1.4.3 Wide-band Receivers for Software-Defined Radio Applications

Typical low noise trans-conductance amplifier (LNTA) first receivers [15, 16] employ a wide-band LNTA followed by a switch-capacitor passive down-conversion mixer as shown in Fig. 1.9. These receiver architectures offer wide-band operation, low noise figure and high conversion gain hence suitable for SDR applications. The working principle and architectural implementation details are explained below.

Figure 1.9: Block diagram of LNA first wideband receiver architecture[16]

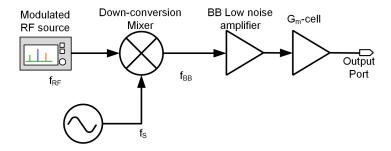

The trans-conductance ( $G_m$ -cell) converts input RF voltage to the corresponding current, and it is fed to a sampling mixer. The down-conversion mixer with a sampling frequency( $f_s$ ) translates the amplified input RF signal with frequency,  $f_{RF}$  to baseband(BB) at the output. The sampling mixer employs a square wave local oscillator hence mixing a signal by a square wave translates blockers/interferers present at the harmonics of  $f_s$  to the baseband, and high conversion gain also amplifies blockers, thereby deteriorating the performance of the receiver. Therefore, to address this issue, multi-path or multi-phase mixing down-conversion mixer topologies are implemented, such as [18], where down-conversion is implemented by three phases  $0^{\circ}$ ,  $45^{\circ}$ ,  $90^{\circ}$  and weighted by  $1:\sqrt{2}:1$ , and summed to generate a sine wave look like LO signal. The advantage of such LO is harmonic rejection since the Fourier coefficient of the third and fifth harmonics of the resultant LO becomes zero. In a similar approach[19], the down-conversion with a weighing factor of  $1:\sqrt{2}:1$  is realized in two stages to improve the harmonic rejection. However,

the main disadvantage of such implementation is achieving irrational weighing gains, and two-stage implementations increase the complexity of the receiver.

#### 1.5 Research Gaps and Thesis Objectives

#### 1.5.1 Research Gaps

Based on the literature survey, this section presents the limitations of the sub-sampling receiver implementations [9–11] and RF sampling-based switch-capacitor receiver implementation [12, 13, 16].

As explained in Section 1.4, the sub-sampling down-conversion [10] employs a single-stage switch-capacitor I/Q down-conversion mixer and IF to BB decimation filter for collecting I/Q samples. Furthermore, the low noise quadrature down-conversion mixer [11] employs transconductor ' $g_m$ ' for converting the input voltage to the corresponding current, thereby implementing current-mode sampling for down-conversion. The dual-band sub-sampling receiver architecture [9] translates both the 2.4 GHz and 5 GHz bands. These implementations have the same drawback of high noise figure and poor linearity. In addition, the sub-sampling receiver implementations are LNA-first receivers and hence do not provide reconfigurability. Conversely, the mixer-first receivers require a sampling frequency greater than or equal to the input RF frequency and provide reconfigurability over a wide frequency range. The switch-capacitor RF front-ends provide high linearity and a good noise figure of 8 dB or less without a traditional LNA. However, the frequency synthesizers employed in these implementations consume high power since the design is complex and operates at a high frequency. The performance of these RF front-end architectures is compared in Table 1.1.

Therefore, from the literature review presented in Section 1.4, it is evident that there is a need for digitally intensive sub-sampling quadrature down-conversion RF front-end architecture with 50  $\Omega$  impedance matching at the RF port. The sub-sampling approach offers a low-power programmable receiver RF front solution for low-power applications since the sampling frequency is less than the input RF, leading to the reduced power consumption of the frequency synthesizer. To address the research gap presented above, the next section presents the proposed digitally intensive sub-sampling receiver architectures.

Table 1.1: Performance summary of the state-of-the-art RF front-ends present in the literature

|                                                | [13]        | [12]      | [20]                            | [21]        | [22]                                                                                       | [23]       | [24]         | [22]        | [10]              | [26]*                                                                                                                              | 3]          | [6]        |

|------------------------------------------------|-------------|-----------|---------------------------------|-------------|--------------------------------------------------------------------------------------------|------------|--------------|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|

| Sampling Scheme                                |             |           |                                 | RF sampling | oling                                                                                      |            |              |             |                   | Sub-Sampling                                                                                                                       | <b>60</b>   |            |

| Architecture                                   |             |           | Mix                             | Mixer-first |                                                                                            |            | LNA-first    |             |                   | LNA-first                                                                                                                          |             |            |

| Impedance matching<br>w/o LNA                  | 50          |           | ·                               | Yes         |                                                                                            |            | No           |             |                   | No                                                                                                                                 |             |            |

| Supply(V)                                      | 1.2/2.5     | 1.2/1.6   | 1.2                             | 1.2         | 4.5/2.5                                                                                    | 1/1.2      | 1.5          | 9.0         | 1.8               | T                                                                                                                                  | 1           | 1.2        |

| $\operatorname{Technology}(\operatorname{nm})$ | 65          | 40        | 65                              | 28          | 130B                                                                                       | 28         | 130          | 99          | 180               | 28                                                                                                                                 | 9           | 65         |

| $f_{RF}({ m GHz})$                             | 0.1-2.4     | 0.1-0.7   | 0.2 - 2                         | 0.2-2       | 2-11                                                                                       | 0.1-2      | 0.8-4        | 2.4/2.7     | 2.4-2.485         | 58.2-64.8                                                                                                                          | 2.4-2.483   | 4.5-5.7    |

| $f_s({ m MHz})$                                | 0.1-2.4     | 0.1-0.7   | 0.2 - 2                         | 0.2-2       | 2-11                                                                                       | 0.1-2      | 0.8-4        | 0.3         | 1072 567          | 37.2-43.6                                                                                                                          | 1.92-1.99   | 1.7-2.15   |

| NF(dB)                                         | 8-9         | 9.8-12.7  | 9.5                             | 7.3-10.6    | 14±1                                                                                       | 7.1-10.3   | 3.8          | 9/2         | NR                | 2                                                                                                                                  | 11.5        | 12         |

| $\mathrm{BW}(\mathrm{MHz})$                    | 20          | 3.2-4.8   | 25                              | 18          | 80-260                                                                                     | 9.9        | 8/9          | 1           | NR                | NR                                                                                                                                 | 20          | 20-77      |

| $IIP_3(dBm)$                                   | $25^a$      | $24^a$    | 11                              | $24^a$      | $20^a$                                                                                     | $35^a$     | -3.5         | NR          | $+5.5 \mid +13.5$ | .5 NR                                                                                                                              | -23 to -8   | -21.5 to 8 |

| Gain(dB)                                       | 40-70       | 40        | 19                              | 40          | 10-24                                                                                      | 16         | 28           | 40          | -1 1              | 36                                                                                                                                 | 26          | 26-40      |